# **DSTni-EX User Guide**

**Section 1**

Part Number 900-335 Revision A 3/04

# **Copyright & Trademark**

© 2003 Lantronix, Inc. All rights reserved.

Lantronix and the Lantronix logo, and combinations thereof are registered trademarks of Lantronix, Inc. DSTni is a registered trademark of Lantronix, Inc. Ethernet is a registered trademark of Xerox Corporation. All other product names, company names, logos or other designations mentioned herein are trademarks of their respective owners.

- Am186 is a trademark of Advanced Micro Devices, Inc.

- Ethernet is a registered trademark of Xerox Corporation.

- SPI is a trademark of Motorola, Inc.

No part of this guide may be reproduced or transmitted in any form for any purpose other than the purchaser's personal use, without the express written permission of Lantronix, Inc.

#### Lantronix

15353 Barranca Parkway Irvine, CA 92618, USA Phone: 949-453-3990 Fax: 949-453-3995

#### Technical Support

Phone: 630-245-1445 Fax: 630-245-1717

#### **Master Distributor**

Grid Connect 1841 Centre Point Circle, Suite 143 Naperville, IL 60563 Phone: 630-245-1445 www.gridconnect.com

Am186 is a trademark of Advanced Micro Devices, Inc. Ethernet is a registered trademark of Xerox Corporation. SPI is a trademark of Motorola, Inc.

| REV | Changes                                     | Released Date |

|-----|---------------------------------------------|---------------|

| А   | Reformat. Add changes from Design Spec. 1.1 | 3-24-04       |

### Warranty

Lantronix warrants each Lantronix product to be free from defects in material and workmanship for a period specified on the product warranty registration card after the date of shipment. During this period, if a customer is unable to resolve a product problem with Lantronix Technical Support, a Return Material Authorization (RMA) will be issued. Following receipt of an RMA number, the customer shall return the product to Lantronix, freight prepaid. Upon verification of warranty, Lantronix will -- at its option -- repair or replace the product and return it to the customer freight prepaid. If the product is not under warranty, the customer may have Lantronix repair the unit on a fee basis or return it. No services are handled at the customer's site under this warranty. This warranty is voided if the customer uses the product in an unauthorized or improper way, or in an environment for which it was not designed.

Lantronix warrants the media containing its software product to be free from defects and warrants that the software will operate substantially according to Lantronix specifications for a period of **60 DAYS** after the date of shipment. The customer will ship defective media to Lantronix. Lantronix will ship the replacement media to the customer.

\* \* \* \*

In no event will Lantronix be responsible to the user in contract, in tort (including negligence), strict liability or otherwise for any special, indirect, incidental or consequential damage or loss of equipment, plant or power system, cost of capital, loss of profits or revenues, cost of replacement power, additional expenses in the use of existing software, hardware, equipment or facilities, or claims against the user by its employees or customers resulting from the use of the information, recommendations, descriptions and safety notations supplied by Lantronix. Lantronix liability is limited (at its election) to:

refund of buyer's purchase price for such affected products (without interest)

repair or replacement of such products, provided that the buyer follows the above procedures.

There are no understandings, agreements, representations or warranties, express or implied, including warranties of merchantability or fitness for a particular purpose, other than those specifically set out above or by any existing contract between the parties. Any such contract states the entire obligation of Lantronix. The contents of this document shall not become part of or modify any prior or existing agreement, commitment or relationship.

For details on the Lantronix warranty replacement policy, go to our web site at <a href="http://www.lantronix.com/support/warranty/index.html">http://www.lantronix.com/support/warranty/index.html</a>

# Contents

| Copyright & Trademark                |  |

|--------------------------------------|--|

| Warranty                             |  |

| Contents                             |  |

| 1: About This User Guide             |  |

| Intended Audience                    |  |

| Conventions                          |  |

| Navigating Online                    |  |

| Organization                         |  |

| 2: Introduction                      |  |

| Design Philosophy                    |  |

| DSTni Architecture                   |  |

| Feature List                         |  |

| Feature Descriptions                 |  |

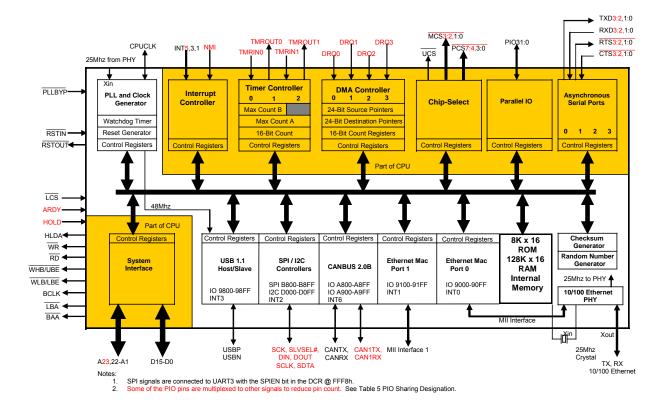

| Block Diagram                        |  |

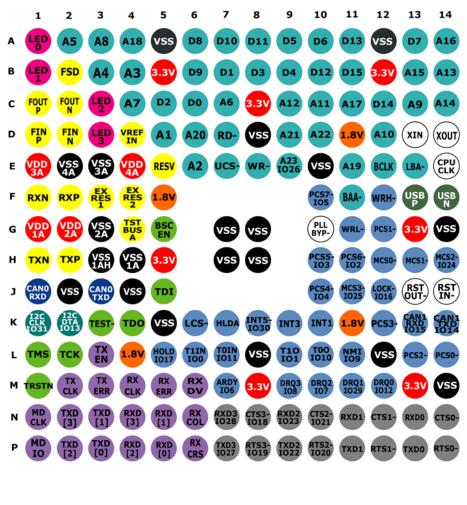

| Ball Assignments                     |  |

| DSTni Ball Descriptions              |  |

| Pin Descriptions by Ball Designation |  |

# 1: About This User Guide

This User Guide describes the technical features and programming interfaces of the Lantronix DSTni-EX chip (hereafter referred to as "DSTni").

DSTni is an Application Specific Integrated Circuit (ASIC)-based single-chip solution (SCS) that integrates the leading-edge functionalities needed to develop low-cost, high-performance device server products. On a single chip, the DSTni integrates an x186 microprocessor, 16K-byte ROM, 256K-byte SRAM, programmable input/output (I/O), and serial, Ethernet, and Universal Serial Bus (USB) connectivity — key ingredients for device- server solutions. Although DSTni embeds multiple functions onto a single chip, it can be easily customized, based on the comprehensive feature set designed into the chip.

Providing a complete device server solution on a single chip enables system designers to build affordable, full-function solutions that provide the highest level of performance in both processing power and peripheral systems, while reducing the number of total system components. The advantages gained from this synergy include:

- Simplifying system design and increased reliability.

- Minimizing marketing and administration costs by eliminating the need to source products from multiple vendors.

- Eliminating the compatibility and reliability problems that occur when combining separate subsystems.

- Dramatically reducing implementation costs.

- Increasing performance and functionality, while maintaining quality and cost effectiveness.

- Streamlining development by reducing programming effort and debugging time.

- Enabling solution providers to bring their products to market faster.

- These advantages make DSTni the ideal solution for designs requiring x86 compatibility; increased performance; serial, programmable I/O, Ethernet, and USB communications; and a glueless bus interface.

## **Intended Audience**

This User Guide is intended for use by hardware and software engineers, programmers, and designers who understand the basic operating principles of microprocessors and their systems and are considering designing systems that utilize DSTni.

## **Conventions**

This User Guide uses the following conventions to alert you to information of special interest.

The symbols # and n are used throughout this Guide to denote active LOW signals.

Notes: Notes are information requiring attention.

## **Navigating Online**

The electronic Portable Document Format (PDF) version of this User Guide contains <u>hyperlinks</u>. Clicking one of these hyper links moves you to that location in this User Guide. The PDF file was created with Bookmarks and active links for the Table of Contents, Tables, Figures and cross-references.

# Organization

This User Guide contains information essential for system architects and design engineers. The information in this User Guide is organized into the following chapters and appendixes.

- <u>Section 1: Introduction</u>

Describes the DSTni architecture, design benefits, theory of operations, ball assignments, packaging, and electrical specifications. This chapter includes a DSTni block diagram.

- <u>Section 2: Microprocessor</u>

Describes the DSTni microprocessor and its control registers.

- <u>Section 2: SDRAM</u>

Describes the DSTni SDRAM and the registers associated with it.

- <u>Section 3: Serial Ports</u>

Describes the DSTni serial ports and the registers associated with them.

- <u>Section 3: Programmable Input/Output</u>

Describes DSTni's Programmable Input/ Output (PIO) functions and the registers associated with them.

- <u>Section 3: Timers</u>

Describes the DSTni timers.

- <u>Section 4: Ethernet Controllers</u> Describes the DSTni Ethernet controllers.

- <u>Section 4: Ethernet PHY</u> Describes the DSTni Ethernet physical layer core.

- <u>Section 5: SPI Controller</u>

Describes the DSTni Serial Peripheral Interface (SPI) controller.

- <u>Section 5: I2C Controller</u> Describes the DSTni I<sup>2</sup>C controller.

- <u>Section 5: USB Controller</u> Describes the DSTni USB controller.

- <u>Section 5: CAN Controllers</u> Describes the DSTni Controller Area Network (CAN) bus controllers.

- <u>Section 6: Interrupt Controller</u> Describes the DSTni interrupt controller.

- <u>Section 6: Miscellaneous Registers</u> Describes DSTni registers not covered in other chapters of this Guide.

- <u>Section 6: Debugging In-circuit Emulator (Delce)</u>

- <u>Section 6: Packaging and Electrical</u> Describes DSTni's packaging and electrical characteristics.

- <u>Section 6: Applications</u> Describes DSTni's packaging and electrical characteristics.

- <u>Section 6: Instruction Clocks</u>

Describes the DSTni instruction clocks.

- <u>Section 6: DSTni Sample Code</u>

- <u>Section 6: Baud Rate Calculations</u>

Provides baud rate calculation tables.

# **2: Introduction**

# **Design Philosophy**

DSTni is a cost-effective, high-performance solution that is the optimized for device server technology board products requiring x86 compatibility, increased performance, and serial, parallel, Ethernet, and/or Universal Serial Bus (USB) connectivity. DSTni integrates the functionality of today's cutting-edge technologies into a robust, cost-effective, embedded single-chip solution (SCS). This approach enables system designers to develop all-in-one, next-generation device server solutions around a single, flexible DSTni chip, with minimum silicon cost and design effort. In this way, DSTni makes it possible to implement a fully functional system — with ROM and RAM; serial, parallel, Ethernet, and USB interfaces; and programmable input/output (PIO) capability — without requiring additional system-interface logic.

DSTni's all-in-one SCS solution reduces development costs and time-to-market by integrating all of the functionality needed to build board-level device server solutions. Even manufacturers that lack the expertise or resources to enter the growing device server marketplace can use DSTni to gain a competitive edge in their market segment.

## **DSTni Architecture**

At the heart of DSTni is an embedded enhanced 80186 microprocessor. As the most widely supported embedded computer architecture in the world, x86 fully leverages the installed base of software drivers, peripheral chips, networking, and communication protocol stacks, and real-time operating systems. It also has the widest performance range of any microprocessor, allowing for a broad range of system implementations and cost targets.

x86-based code inherently uses less memory than equivalent RISC-based code, so less physical memory is required in an end system for the same application. And because x86 is the same industry-standard architecture used on PCs, existing x86 assembly language can be ported to the DSTni with minimal modifications.

**Note:** I/O registers and peripherals internal to DSTni are word registers unless otherwise defined. They should be only written as words. Peripherals outside DSTni can be written as either bytes or words.

# Feature List

- Embedded Phase Lock Loop (PLL) 1-115x

- Embedded enhanced 80186 CPU (1 to 115 MHz)

- Embedded enhanced 80186 peripherals

- Embedded Ethernet controllers

- Enhanced 32-byte-deep transmit FIFOs

- One MII interface port 0 with 10/100 Mbit PHY transceiver (includes 100Base-FX)

- Second MII interface port 1

- Embedded boot code

- 16K bytes of ROM (8K x 16)

- Embedded Synchronous Random Access Memory (SRAM)

- 256K bytes of 0 wait state SRAM (128K x 16)

- Embedded Burst/Page Access Upper Chip Select (UCS)

- Four 186ES-compatible serial ports

- Enhanced receive FIFOs (4 deep)

- Additional handshake control

- Two CANBUS 2.0b controllers

- One Universal Serial Bus (USB) 1.1 Controller

- One 3-wire Serial Peripheral Interface (SPI) controller

- One 2-wire I<sup>2</sup>C serial controller

- Single input clock (25 MHz)

- 16-bit random-number generator

- 16-bit TCP/IP checksum generator

- SDRAM memory interface (16, 64, and 128 Mbit)

- Temperature range: –40°C to 85°C ambient

- Package 12x12 mm 184 BGA

# Feature Descriptions

### Software-Controlled Clock

DSTni comes with a phase-lock loop that can be programmed from 1 to 115 MHz. This feature allows DSTni to be run at a variety of clock frequency combinations, up to 115 MHz, while keeping power consumption to an absolute minimum. The clock defaults to 24 MHz on power-up or reset. As a result, DSTni can be scaled to perform tasks at the speed ideally suited for those tasks, thereby minimizing power consumption and heat generation and conserving energy.

### **Small Footprint**

DSTni has a footprint of 12 mm<sup>2</sup>. DSTni's Ball Grid Array (BGA) package provides a significant reduction in board real estate. This allows DSTni to fit the most tightly populated products. DSTni also boasts a glueless logic architecture for a seamless hardware interface.

### Four Asynchronous Serial Ports

DSTni provides four identical asynchronous serial ports. Each port operates independently and has the following features:

- Full-duplex operation

- Programmable baud-rate generator

- 7-, 8-, or 9-bit operation

- Even, odd, or no parity

- 1 or 2 stop bits:

1 stop bit for 7-, 8-, or 9-bit operation

2 stop bits for 7- or 8-bit operation

- Direct Memory Access (DMA) to and/or from serial ports

- Hardware flow control

- Transmit and detect break characters

- Programmable interrupt generation for break characters and data words

### **DMA and Serial Ports**

Each DSTni serial port can use its own DMA channel, allowing for direct DMA to and from the serial port. DMA transfers to a serial port are destination synchronized; DMA transfers from a serial port are source synchronized, with a new request generated when data is present in the receive FIFO.

**Note:** A total of 4 DMA channels are available. Typically, if four serial channels are used, one DMA channel is placed on each receive channel.

### **Two Ethernet Controllers**

DSTni supports two IEEE-compliant Ethernet controllers:

- One controller has the PHY transceiver connected to it. This controller works in 10/ 100 Mbit (10Base-T and 100Base-TX) mode and supports 100Base-FX mode (100 Mbit over two fiber-optic cables).

- The other controller has an external MII interface.

The internal PHY supports half- and full-duplex operation, with full-featured auto-negotiation functionality.

#### **CANBUS 2.0b Controllers**

DSTni provides two CANBUS 2.0b controllers that filter incoming messages by identifier or by data. Messages that do not pass the controller's filtering mechanism are not passed to the microprocessor, saving CPU bandwidth.

#### **USB 1.1 Controller**

DSTni supports a USB 1.1 controller, which is fully compliant as a device. The controller supports 8 bidirectional endpoints, along with DMA or First In First Out (FIFO) data stream interfaces. The USB controller also provides host-mode logic for emulating a PC host.

#### **SPI Serial Controller**

DSTni provides a 3-wire SPI serial controller that supports "master" and "slave" devices, as well as multiple-master and multiple-slave devices. The SPI interface detects collisions when multiple masters try to transfer data at the same time, and is completely software programmable.

#### I<sup>2</sup>C Serial Controller

DSTni provides a 2-wire  $I^2C$  serial controller that provides an interface between the DSTni microprocessor and an  $I^2C$  bus. It can be used in applications involving  $I^2C$  bus devices, including those that use the  $I^2C$  bus as a board-level communications protocol.

The controller can be programmed to operate as either a master or slave device.

- In master mode, the controller performs the required arbitration for operation in multimaster systems.

- In slave mode, the controller can interrupt the microprocessor when it recognizes its own 7- or 10-bit address or the general call address.

#### Watchdog Timer

DSTni provides a watchdog timer that can be configured to generate either an NMI interrupt or a system reset upon timeout. After reset, the watchdog timer defaults to the setting specified by bit [12] of the DSTni Configuration register (see page **Error! Bookmark not defined.**). It can be modified or disabled only one time.

If the timer is not disabled, the application program must periodically reset the timer by writing a specific key sequence to the watchdog timer control register. If the timer is not reset before it counts down, either an NMI or a system reset is issued, depending on the configuration of the timer.

#### **Standards Compliance**

DSTni supports multiple worldwide standards including:

- IEEE 802.3, 802.3u, and 802.3af Ethernet standards

- CANBUS 2.0b

- USB 1.1

# **Block Diagram**

#### Figure 2-1. DSTni Block Diagram

## **Ball Assignments**

### **DSTni Ball Diagram**

Figure 2-2. DSTni Ball Grid Array Looking through Top of Package

# DSTni Ball Descriptions

| Ball Pin<br>Name | Ball Pin                                         | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |

|------------------|--------------------------------------------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Hamo             | Host Interface<br>(All Pins are 5 Volt Tolerant) |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |

| CPUCLK           | E14                                              | I/O  | <b>CPU Clock Output</b> (24ma)<br>This pin is driven from the output of the internal PLL. This output pin can be<br>three-stated by setting the CD bit in the SYSCON register. When the PLL is<br>bypassed, this pin is tri-stated and is the CPUCLK input source.                                                                                                                                                                                                                                                                                      |  |  |  |  |

| PLLBYP#          | G10                                              | IN   | <b>PLL Bypass Input</b> (Active LOW with Pull-up)<br>This input, when pulled LOW, bypasses the internal PLL and uses the<br>CPUCLK pin as the source for the CPU.                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

| WR#              | E8                                               | OUT  | Write Output (16ma Active LOW with Pull-up)<br>This pin indicates that the current bus cycle is a memory or I/O write cycle.                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

| RD#              | D7                                               | I/O  | <b>Read Output</b> (16ma Active LOW with Pull-up)<br>This pin indicates that the current bus cycle is a memory or I/O read cycle. If<br>HLDA is active, this pin is used as an input to read data from the internal<br>256K bytes of SRAM.                                                                                                                                                                                                                                                                                                              |  |  |  |  |

| WRH#             | F12                                              | I/O  | Write High Output (16ma Active Low with Pull-up)<br>IF CSBE is set to '1' in the DCR, this pin indicates that the current bus cycle<br>is a memory or I/O write cycle and that the upper byte is being driven with<br>valid data. IF CSBE is set to '0' in the DCR, this pin indicates the upper byte<br>chip select is valid. If HLDA is active, this pin is used as an input to enable<br>writing data to the upper byte of the internal 256K bytes of SRAM.                                                                                          |  |  |  |  |

| WRL#             | G11                                              | I/O  | Write Low Output (16ma Active LOW with Pull-up)<br>IF CSBE is set to '1' in the DCR, this pin indicates that the current bus cycle<br>is a memory or I/O write cycle and that the lower byte is being driven with<br>valid data. If CSBE is set to '0' in the DCR, this pin indicates the lower byte<br>chip select is valid. If HLDA is active, this pin is used as an input to enable<br>writing data to the lower byte of the internal 256K bytes of SRAM.                                                                                           |  |  |  |  |

| UCS#             | E7                                               | OUT  | <b>Upper Memory Chip Select Output</b> (4ma Active LOW)<br>This pin indicates to the system that a memory access is in progress to the<br>upper memory block. The base address and size of the upper memory block<br>are programmable up to 1 Mbyte (20-bit address mode) or up to 16 Mbyte<br>(24-bit address mode). Upper memory chip select is always configured for<br>16bit bus size. After reset, UCS# is active for the 64 Kbyte memory range<br>from F0000h to FFFFFh (20-bit address mode) or from FF0000h to FFFFFh<br>(24-bit address mode). |  |  |  |  |

| HLDA             | К7                                               | OUT  | <b>Hold Acknowledge</b> (4ma Active HIGH)<br>This pin goes HIGH to indicate the bus has been released for use by an<br>external bus master. The internal 256K bytes of internal memory is the only<br>peripheral that can be accessed by an external bus master. The bus is<br>requested using the HOLD pin (multiplexed on IO17).                                                                                                                                                                                                                      |  |  |  |  |

| LCS#             | K6                                               | IN   | <b>Lower Chip Select</b> (Schmitt Trigger Input Active LOW with Pull-up)<br>This pin is used by an external bus master to enable reading and writing the<br>internal 256K bytes of SRAM.                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| LBA#             | E13                                              | OUT  | <b>Load Burst Address Output</b> (12ma Active LOW)<br>This pin, when LOW, causes the burst flash memory device to load a new<br>memory address from which to access memory cycles. This means a burst<br>miss has occurred.                                                                                                                                                                                                                                                                                                                             |  |  |  |  |

| BAA#             | F11                                              | OUT  | <b>Burst Address Advance Output</b> (12ma Active LOW)<br>This pin, when LOW, causes the burst flash memory device to increment the<br>internal memory address from which to access memory cycles. This means<br>a burst hit has occurred.                                                                                                                                                                                                                                                                                                               |  |  |  |  |

### Table 2-1. DSTni Ball Descriptions by Pin Name

| Ball Pin<br>Name                                                                                                                                  | Ball Pin                                                                                           | Туре                     | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|---------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|--------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BCLK                                                                                                                                              | E12                                                                                                | OUT                      | <b>Burst Clock Output</b> (12ma Active HIGH)<br>This pin, when clocking from LOW to HIGH, causes the burst flash memory<br>device to process any commands determined by the LBA# or BAA# pins.<br>This pin only transitions when burst flash is enabled and one of the flash<br>control signals has changed.                                                                                                                                                                                                                                                                                    |

| MCS[1]#<br>MCS[0]#                                                                                                                                | H13<br>H12                                                                                         | OUT<br>OUT               | <b>Middle Memory Chip Select Output</b> (8ma Active LOW)<br>These pins indicate to the system that a memory access is in progress to the<br>midrange memory block. The base address and size of the mid-range<br>memory block are programmable. The Middle memory chip selects are<br>always configured for 16bit bus size. MCS[0]# can be programmed as the<br>chip select for the entire middle chip select address range. MCS[0] is also<br>used as CS_n for connecting a SDRAM externally.                                                                                                  |

| PCS[3]#<br>PCS[2]#<br>PCS[1]#<br>PCS[0]#                                                                                                          | K12<br>L13<br>G12<br>L14                                                                           | OUT<br>OUT<br>OUT<br>OUT | <b>Peripheral Chip Select Output</b> (8ma Active LOW)<br>These pins indicate to the system that a bus cycle is in progress to the<br>corresponding region of the peripheral space. The base address of the<br>peripheral block is programmable.                                                                                                                                                                                                                                                                                                                                                 |

| RSTIN#                                                                                                                                            | J14                                                                                                | IN                       | <b>Reset Input</b> (Schmitt Trigger Input, Active LOW with Pull-up)<br>This pin causes the CPU to perform a reset. When this pin is asserted, the<br>CPU immediately terminates any current bus cycles, resets internal logic and<br>prepares for executing code at the reset address. FFFF0h in 20bit mode<br>and FFFFE0h in 24bit mode.<br>RSTIN# is synchronized internally and extended internally to allow ~200 ms<br>for the DCR and RCR to settle to the values driven by there individual<br>resistors. This input is provided with a Schmitt trigger to power-on via an RC<br>network. |

| RSTOUT#                                                                                                                                           | J13                                                                                                | OUT                      | <b>Reset Output</b> (4ma Active LOW)<br>This pin indicates whether the CPU is being reset. It indicates that the<br>internal logic is being reset and is to be used to reset any external<br>peripherals.                                                                                                                                                                                                                                                                                                                                                                                       |

| DB[15]<br>DB[14]<br>DB[12]<br>DB[12]<br>DB[10]<br>DB[9]<br>DB[9]<br>DB[8]<br>DB[7]<br>DB[6]<br>DB[5]<br>DB[4]<br>DB[3]<br>DB[2]<br>DB[1]<br>DB[0] | B11<br>C12<br>A11<br>B10<br>A8<br>A7<br>B6<br>A6<br>A13<br>A10<br>A9<br>B9<br>B8<br>C5<br>B7<br>C6 | I/O                      | <b>CPU Data Bus</b> (8ma Active HIGH with Pull-downs)<br>These pins supply the data to the memory or I/O of the system. The state of<br>these pins are also latched into the Reset Configuration Register (RCR) prior<br>to RSTOUT being de-asserted. External pull-up resistors can be placed on<br>this bus to set the corresponding bit in the RCR.                                                                                                                                                                                                                                          |

| Ball Pin                                                   | Ball Pin                            | Туре                                               | Description                                                                                                                                                                                                                                                                                                                        |

|------------------------------------------------------------|-------------------------------------|----------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Name<br>A[22]<br>A[21]<br>A[20]<br>A[19]<br>A[18]<br>A[17] | D10<br>D9<br>D6<br>E11<br>A4<br>C11 | I/O 1<br>I/O 1<br>I/O 1<br>I/O 0<br>I/O 0<br>I/O 0 | Address Bus (8ma with Pull-ups and Pull-downs)<br>These pins supply the address to memory or I/O of the system. If HLDA is<br>active, A17-1 are used to access the internal 256K bytes of internal SRAM.<br>The other address pins are ignored.<br>Just prior to RSTOUT being de-asserted, these pins program the DCR<br>register. |

| A[16]                                                      | A14                                 | I/O 0                                              | A22 BOOTROM Default                                                                                                                                                                                                                                                                                                                |

| A[15]                                                      | B13                                 | I/O 1                                              | 0 Disabled                                                                                                                                                                                                                                                                                                                         |

| A[14]                                                      | C14                                 | I/O 1                                              | 1 Enabled *                                                                                                                                                                                                                                                                                                                        |

| A[13]                                                      | B14<br>C9                           | I/O 1<br>I/O 1                                     |                                                                                                                                                                                                                                                                                                                                    |

| A[12]<br>A[11]                                             | C9<br>C10                           | 1/0 0                                              | A21 Address Mode Default                                                                                                                                                                                                                                                                                                           |

| A[10]                                                      | D12                                 | I/O 0                                              | 0 20 Bit<br>1 24 Bit *                                                                                                                                                                                                                                                                                                             |

| A[9]                                                       | C13                                 | I/O 0                                              |                                                                                                                                                                                                                                                                                                                                    |

| A[8]                                                       | A3                                  | I/O 0                                              | A20 Watchdog Default                                                                                                                                                                                                                                                                                                               |

| A[7]                                                       | C4<br>C7                            | I/O 0<br>I/O 0                                     | 0 Disabled                                                                                                                                                                                                                                                                                                                         |

| A[6]<br>A[5]                                               | A2                                  | I/O 0                                              | 1 Enabled *                                                                                                                                                                                                                                                                                                                        |

| A[4]                                                       | B3                                  | 1/0 0                                              |                                                                                                                                                                                                                                                                                                                                    |

| A[3]                                                       | B4                                  | I/O 0                                              | A18 SPI Default                                                                                                                                                                                                                                                                                                                    |

| A[2]                                                       | E6                                  | I/O 0                                              | 0 Disabled *<br>1 Enabled                                                                                                                                                                                                                                                                                                          |

| A[1]                                                       | D5                                  | I/O 0                                              | 1 Enabled                                                                                                                                                                                                                                                                                                                          |

|                                                            |                                     |                                                    | A19, [17:8] are used in various ways by internal boot routines.<br>A7-1 are used for ASIC production testing only. Leave at '0'.<br>In 20-bit address mode, A20-23 are not used and return '0'.                                                                                                                                    |

| INT3                                                       | K9                                  | IN                                                 | In 20-bit address mode, A20-23 always return '0' during code execution. Interrupt In (Schmitt Trigger Input, Active HIGH with Pull-down)                                                                                                                                                                                           |

| INT1                                                       | K10                                 | IN                                                 | These pins are external interrupt input requests. INT3 is OR'ed with the USB controller at interrupt type 15. INT1 is OR'ed with the MAC 1 controller                                                                                                                                                                              |

|                                                            |                                     |                                                    | at interrupt type 13.<br>UART0 Interface                                                                                                                                                                                                                                                                                           |

| TXD0                                                       | P13                                 | OUT                                                | Transmit Data 0 Out (2ma)                                                                                                                                                                                                                                                                                                          |

|                                                            |                                     |                                                    | This pin provides serial transmit data to the system from serial port 0.                                                                                                                                                                                                                                                           |

| RXD0                                                       | N13                                 | IN                                                 | <b>Receive Data 0 In</b> (Schmitt Trigger Input, Active HIGH with Pull-up)<br>This pin provides serial receive data from the system to serial port 0.                                                                                                                                                                              |

| RTS0#                                                      | P14                                 | OUT                                                | <b>Ready to Send 0 Out</b> (2ma)<br>This pin provides the Ready to Send output for serial port 0. This pin<br>provides the handshaking output for serial port 0.                                                                                                                                                                   |

| CTS0#                                                      | N14                                 | IN                                                 | <b>Clear to Send 0 In</b> (Schmitt Trigger Input, Active High with Pull up)<br>This pin provides the Clear to Send input for serial port 0. This pin provides the handshaking input for serial port 0.                                                                                                                             |

|                                                            |                                     |                                                    | UART1 Interface                                                                                                                                                                                                                                                                                                                    |

| TXD1                                                       | P11                                 | OUT                                                | Transmit Data 1 Out (2ma)<br>This pin provides serial transmit data to the system from serial port 1.                                                                                                                                                                                                                              |

| RXD1                                                       | N11                                 | IN                                                 | <b>Receive Data 1 In</b> (Schmitt Trigger Input, Active HIGH with Pull-up)<br>This pin provides serial receive data from the system to serial port 1.                                                                                                                                                                              |

| RTS1#                                                      | P12                                 | OUT                                                | <b>Ready to send 1 Out</b> (2ma)<br>This pin provides the Ready to Send output for serial port 1. This pin provides the handshaking output for serial port 1.                                                                                                                                                                      |

| CTS1#                                                      | N12                                 | IN                                                 | <b>Clear to Send 1 In</b> (Schmitt Trigger Input, Active HIGH with Pull-up)<br>This pin provides the Clear to Send input for serial port 1. This pin provides the handshaking input for serial port 1.                                                                                                                             |

|                                                            |                                     |                                                    | Parallel Interface                                                                                                                                                                                                                                                                                                                 |

| PIO31                                                      | K1                                  | I/O                                                | Parallel I/O Bit [31] Pin (4ma Schmitt Input with Pull-up)                                                                                                                                                                                                                                                                         |

| I2CCLK                                                     |                                     | I/O                                                | This pin corresponds to bit [31] of the PIO register.<br>This pin can also be used with the I <sup>2</sup> C block as the CLK if PIO bit [31] is<br>programmed for normal operation.                                                                                                                                               |

| Ball Pin<br>Name      | Ball Pin | Туре              | Description                                                                                                                                                                                                                                                                                                                                                                                                                         |

|-----------------------|----------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PIO30<br>INT5#        | K8       | I/O<br>IN         | Parallel I/O Bit [30] Pin (4ma Schmitt Input with Pull-up)<br>This pin corresponds to bit [30] of the PIO register.<br>This pin can also be used as INT5 when PIO30 is programmed for normal<br>operation. Note: This interrupt is shared with UART 3.                                                                                                                                                                              |

| PIO29<br>DRQ1         | M11      | I/O<br>IN         | Parallel I/O Bit [29] and DRQ1 Pin (4ma Schmitt Input with Pull-up)<br>This pin corresponds to bit [29] of the PIO register.<br>This pin can also be used as DMA request 1 with the DMA if PIO bit [29] is<br>programmed for normal operation.                                                                                                                                                                                      |

| PIO28<br>RXD3<br>MOSI | N7       | I/O<br>IN<br>OUT  | <ul> <li>Parallel I/O Bit [28] Pin (4ma Schmitt Input with Pull-up)<br/>This pin corresponds to bit [28] of the PIO register.<br/>This pin can also be used with:</li> <li>UART 3 as receive data (RXD3) if PIO bit [28] is programmed for normal operation.</li> <li>The SPI controller if the SPIEN bit is set in the DCR register.<br/>This pin connects to the serial data in (SDI) of an external SPI device.</li> </ul>       |

| PIO27<br>TXD3<br>MISO | P7       | I/O<br>OUT<br>IN  | <ul> <li>Parallel I/O Bit [27] Pin (4ma Schmitt Input with Pull-up)<br/>This pin corresponds to bit [27] of the PIO register.<br/>This pin can also be used with:</li> <li>UART 3 as transmit data (TXD3) if PIO bit [27] is programmed for<br/>normal operation.</li> <li>The SPI controller if the SPIEN bit is set in the DCR register.<br/>This pin connects to the serial data out (SDO) of an external SPI device.</li> </ul> |

| PIO26<br>A23          | E9       | I/O<br>OUT        | Parallel I/O Bit [26] Pin (4ma Schmitt Input with Pull-up)<br>This pin corresponds to bit [26] of the PIO register.<br>This pin can also be used as address line 23 (A23) if PIO bit [26] is<br>programmed for normal operation.                                                                                                                                                                                                    |

| PIO25<br>MCS3#        | J11      | I/O<br>OUT        | <b>Parallel I/O Bit [25] Pin</b> (4ma Schmitt Input with Pull-up)<br>This pin corresponds to bit [25] of the PIO register.<br>This pin can also be used as middle chip select 3 (MCS3#) if PIO bit [25] is<br>programmed for normal operation.                                                                                                                                                                                      |

| PIO24<br>MCS2#        | H14      | I/O<br>OUT        | <b>Parallel I/O Bit [24] Pin</b> (4ma Schmitt Input with Pull-up)<br>This pin corresponds to bit [24] of the PIO register.<br>This pin can also be used as middle chip select 2 (MCS2#) if PIO bit [24] is<br>programmed for normal operation.                                                                                                                                                                                      |

| PIO23<br>RXD2         | N9       | I/O<br>IN         | Parallel I/O Bit [23] Pin (4ma Schmitt Input with Pull-up)<br>This pin corresponds to bit [23] of the PIO register.<br>This pin can also be used with UART 2 as receive data (RXD2) if PIO bit [23]<br>is programmed for normal operation.                                                                                                                                                                                          |

| PIO22<br>TXD2         | P9       | I/O<br>OUT        | Parallel I/O Bit [22] Pin (4ma Schmitt Input with Pull-up)<br>This pin corresponds to bit [22] of the PIO register.<br>This pin can also be used with UART 2 as transmit data (TXD2) if PIO bit<br>[22] is programmed for normal operation.                                                                                                                                                                                         |

| PIO21<br>CTS2#        | N10      | I/O<br>IN         | Parallel I/O Bit [21] Pin (4ma Schmitt Input with Pull-up)<br>This pin corresponds to bit [21] of the PIO register.<br>This pin can also be used with UART 2 as Clear to Send (CTS2#) if PIO bit<br>[21] is programmed for normal operation.                                                                                                                                                                                        |

| PIO20<br>RTS2#        | P10      | I/O<br>OUT        | Parallel I/O Bit [20] Pin (4ma Schmitt Input with Pull-up)<br>This pin corresponds to bit [20] of the PIO register.<br>This pin can also be used with UART 2 as ready to send (RTS2#) if PIO bit<br>[20] is programmed for normal operation.                                                                                                                                                                                        |

| PIO19<br>RTS3#<br>SCK | P8       | I/O<br>OUT<br>I/O | <ul> <li>Parallel I/O Bit [19] Pin (4ma Schmitt Input with Pull-up)<br/>This pin corresponds to bit [19] of the PIO register.<br/>This pin can also be used with:</li> <li>UART 3 as ready to send (RTS3#) if PIO bit [19] is programmed for<br/>normal operation.</li> <li>The SPI controller if the SPIEN bit is set in the DCR register.<br/>This pin connects to the serial clock (SCK) of the SPI controller.</li> </ul>       |

| Ball Pin<br>Name          | Ball Pin | Туре              | Description                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|---------------------------|----------|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PIO18<br>CTS3#<br>SLVSEL  | N8       | I/O<br>IN<br>IN   | <ul> <li>Parallel I/O Bit [18] Pin (4ma Schmitt Input with Pull-up)</li> <li>This pin corresponds to bit [18] of the PIO register.</li> <li>This pin can also be used with:</li> <li>UART 3 as clear to send (CTS3#) if PIO bit [18] is programmed for normal operation.</li> <li>The SPI controller if the SPIEN bit is set in the DCR register.</li> <li>This pin connects to the slave select output (SLVSEL) of the SPI controller.</li> </ul> |

| PIO17<br>HOLD             | L5       | I/O<br>IN         | Parallel I/O Bit [17] Pin (4ma Schmitt Input with Pull-up)<br>This pin corresponds to bit [17] of the PIO register.<br>This pin can also be used as the HOLD input if PIO bit [17] is programmed<br>for normal operation. When driven HIGH by an external bus master, the<br>CPU responds with HLDA and releases the bus for external use. Only the<br>internal 256K bytes of memory are accessible externally.                                    |

| PIO16<br>LOCK#<br>SRDYOUT | J12      | I/O<br>OUT<br>OUT | Parallel I/O Bit [16] Pin (4ma Schmitt Input with Pull-up)<br>This pin corresponds to bit [16] of the PIO register.<br>This pin can also be used as the CPU bus lock# output. If the SRDYOUT bit<br>in the PLL/CLK register is set to '1', this pin outputs the internal SRDY signal<br>for wait state debug use.                                                                                                                                  |

| PIO15<br>CAN1RXD          | K13      | I/O<br>IN         | Parallel I/O Bit [15] Pin (4ma Schmitt Input with Pull-up)<br>This pin corresponds to bit [15] of the PIO register.<br>This pin can also be used as CAN controller 1 receive if PIO bit [15] is<br>programmed for normal operation.                                                                                                                                                                                                                |

| PIO14<br>CAN1TXD          | K14      | I/O<br>OUT        | Parallel I/O Bit [14] Pin (4ma Schmitt Input with Pull-up)<br>This pin corresponds to bit [14] of the PIO register.<br>This pin can also be used as CAN controller 1 transmit if PIO bit [14] is<br>programmed for normal operation.                                                                                                                                                                                                               |

| PIO13<br>I2CDTA           | K2       | I/O               | <b>Parallel I/O Bit [13] Pin</b> (4ma Schmitt Input with Pull-up)<br>This pin corresponds to bit [13] of the PIO register.<br>This pin can also be used with the I <sup>2</sup> C block as the I2CDTA if PIO bit [13] is<br>programmed for normal operation.                                                                                                                                                                                       |

| PIO12<br>DRQ0             | M12      | I/O<br>IN         | <b>Parallel I/O Bit 12 Pin</b> (4ma Schmitt Input with Pull-up)<br>This pin corresponds to bit [12] of the PIO register.<br>This pin can also be used with DMA channel 0 as DRQ0 if PIO bit [12] is<br>programmed for normal operation.                                                                                                                                                                                                            |

| PIO0<br>TMR1IN            | L6       | I/O<br>IN         | <b>Parallel I/O Bit [0] Pin</b> (4ma Schmitt Input with Pull-up)<br>This pin corresponds to bit [0] of the PIO register.<br>This pin can also be used with Timer Channel 1 as TMR1IN if PIO bit [0] is<br>programmed for normal operation.                                                                                                                                                                                                         |

| PIO11<br>TMR0IN           | L7       | I/O<br>IN         | <b>Parallel I/O Bit 11 Pin</b> (4ma Schmitt Input with Pull-up)<br>This pin corresponds to bit [11] of the PIO register.<br>This pin can also be used with Timer Channel 0 as TMR0IN if PIO bit [11] is<br>programmed for normal operation.                                                                                                                                                                                                        |

| PIO10<br>TMR0OUT          | L10      | I/O<br>OUT        | <b>Parallel I/O Bit [10] Pin</b> (4ma Schmitt Input with Pull-up)<br>This pin corresponds to bit [10] of the PIO register.<br>This pin can also be used with Timer Channel 0 as TMR0OUT if PIO bit [10]<br>is programmed for normal operation.                                                                                                                                                                                                     |

| PIO9<br>NMI               | L11      | I/O<br>IN         | <b>Parallel I/O Bit [9] Pin</b> (4ma Schmitt Input with Pull-up)<br>This pin corresponds to bit [9] of the PIO register.<br>This pin can also be used with NMI input if PIO bit [9] is programmed for<br>normal operation.                                                                                                                                                                                                                         |

| PIO8<br>DRQ3              | M9       | I/O<br>IN         | Parallel I/O Bit [8] Pin (4ma Schmitt Input with Pull-up)<br>This pin corresponds to bit [8] of the PIO register.<br>This pin can also be used with DMA channel 3 as DRQ3 if PIO bit [8] is<br>programmed for normal operation.                                                                                                                                                                                                                    |

| PIO7<br>DRQ2              | M10      | I/O<br>IN         | <b>Parallel I/O Bit [7] Pin</b> (4ma Schmitt Input with Pull-up)<br>This pin corresponds to bit [7] of the PIO register.<br>This pin can also be used with DMA channel 2 as DRQ2 if PIO bit [7] is<br>programmed for normal operation.                                                                                                                                                                                                             |

| Ball Pin<br>Name | Ball Pin | Туре | Description                                                                                                                                     |

|------------------|----------|------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| PIO6             | M7       | I/O  | Parallel I/O Bit 6 Pin (4ma Schmitt Input with Pull-up)                                                                                         |

| ARDY             |          | IN   | This pin corresponds to bit [6] of the PIO register.                                                                                            |

|                  |          |      | This pin can also be used with an external ready source ARDY if PIO bit [6]                                                                     |

|                  |          |      | is programmed for normal operation. ARDY is double synchronized                                                                                 |

|                  |          |      | internally using the falling edge of CPUCLK. It can be used to extend                                                                           |

| PIO5             | F10      | I/O  | external accesses if enabled by the appropriate registers (External Ready).<br><b>Parallel I/O Bit [5] Pin</b> (4ma Schmitt Input with Pull-up) |

| PCS7#            | FIU      | OUT  | This pin corresponds to bit [5] of the PIO register.                                                                                            |

| 1031#            |          | 001  | This pin can also be used as peripheral chip select 7 (PCS7#) if PIO bit [5] is                                                                 |

|                  |          |      | programmed for normal operation.                                                                                                                |

| PIO4             | J10      | I/O  | Parallel I/O bit 4 Pin (4ma Schmitt Input with Pull-up)                                                                                         |

| PCS4#            |          | OUT  | This pin corresponds to bit [4] of the PIO register.                                                                                            |

|                  |          |      | This pin can also be used as peripheral chip select 4 (PCS4#) if PIO bit [4] is                                                                 |

|                  |          |      | programmed for normal operation.                                                                                                                |

| PIO3             | H10      | I/O  | Parallel I/O Bit [3] Pin (4ma Schmitt Input with Pull-up)                                                                                       |

| PCS5#            |          | OUT  | This pin corresponds to bit [3] of the PIO register.                                                                                            |

|                  |          |      | This pin can also be used as peripheral chip select 5 (PCS5#) if PIO bit [3] is programmed for normal operation.                                |

| PIO2             | H11      | I/O  | Parallel I/O Bit [2] Pin (4ma Schmitt Input with Pull-up)                                                                                       |

| PCS6#            |          | OUT  | This pin corresponds to bit [2] of the PIO register.                                                                                            |

|                  |          | 001  | This pin can also be used as peripheral chip select 6 (PCS6#) if PIO bit [2] is                                                                 |

|                  |          |      | programmed for normal operation.                                                                                                                |

| PIO1             | L9       | I/O  | Parallel I/O bit [1] Pin (4ma Schmitt Input with Pull-up)                                                                                       |

| TMR10UT          |          | OUT  | This pin corresponds to bit [1] of the PIO register.                                                                                            |

|                  |          |      | This pin can also be used with Timer Channel 1 as TMR1OUT if PIO bit [1] is                                                                     |

|                  |          |      | programmed for normal operation.                                                                                                                |

|                  | 10       |      | AN Bus 0 Interface (External Transceiver)                                                                                                       |

| CANTXD           | J3       | OUT  | CAN Transmit (2ma)                                                                                                                              |

| CANRXD           | J1       | IN   | This pin connects to an external CAN transceiver transmit pin.<br>CAN Receiver (Schmitt Input with Pull-up)                                     |

| CANKAD           | JI       | IIN  | This pin connects to an external CAN transceiver receive pin.                                                                                   |

|                  |          |      | USB Interface                                                                                                                                   |

| USBP             | F13      | I/O  | USB 1.1 Plus                                                                                                                                    |

| 000              | 1.10     |      | USB Transceiver Positive Signal                                                                                                                 |

| USBN             | F14      | I/O  | USB 1.1 Negative                                                                                                                                |

|                  |          |      | USB Transceiver Negative Signal                                                                                                                 |

|                  |          |      | Ethernet 0 Interface (Internal PHY)                                                                                                             |

| XIN              | D13      | IN   | Ethernet Clock (25 MHz Crystal)                                                                                                                 |

| XOUT             | D14      | OUT  | These pins provide the connections for a fundamental mode parallel-                                                                             |

|                  | A 1      |      | resonant crystal.                                                                                                                               |

| LED0             | A1       | OUT  | LED0 Driver (8ma)                                                                                                                               |

| LED1             | B1       | OUT  | LED1 Driver (8ma)                                                                                                                               |

| LED2             | C3       | OUT  | LED2 Driver (8ma)                                                                                                                               |

| LED3             | D3       | OUT  | LED3 Driver (8ma)                                                                                                                               |

| TXP              | H2       | OUT  | Ethernet Transmit Plus                                                                                                                          |

| TXN              | H1       | OUT  | Ethernet Transmit Negative                                                                                                                      |

| RXP              | F2       | IN   | Ethernet Receive Plus                                                                                                                           |

| RXN              | F1       | IN   | Ethernet Receive Negative                                                                                                                       |

| EXRES1           | F3       | I/O  | Ethernet Current Source 1 (12.4K 1% resistor Pin1)                                                                                              |

| EXRES2           | F4       | I/O  | Ethernet Current Source 2 (12.4K 1% resistor Pin 2)                                                                                             |

| TSTBUSA          | G4       | I/O  | <b>Test BUS A</b> (for factory testing of PHY only; leave unconnected)                                                                          |

| .01200/(         |          |      |                                                                                                                                                 |

| Ball Pin<br>Name | Ball Pin   | Туре   | Description                                                                           |

|------------------|------------|--------|---------------------------------------------------------------------------------------|

| Traine           |            |        | Ethernet 0 Fiber Interface (Internal PHY)                                             |

| FSD              | B2         | IN     | Fiber Signal Detect (Schmitt Trigger Input with Pull-down)                            |

| FOUTP            | C1         | OUT    | Fiber Transmit Data Plus (PECL voltage levels)                                        |

| FOUTN            | C2         | OUT    | Fiber Transmit Data Negative (PECL voltage levels)                                    |

| FINP             | D1         | IN     | Fiber Receive Data Plus (PECL voltage levels)                                         |

| FINN             | D2         | IN     | Fiber Receive Data Negative (PECL voltage levels)                                     |

| RESV             | E5         | IN     | Reference Current Resistor Input (1.24K 1% resistor to VSS)                           |

| VREF             | D4         | IN     | Voltage Reference Input (1.235V reference voltage)                                    |

|                  | 51         |        | PHY Power (Internal PHY)                                                              |

| VDD1A            | G1         | PWR    | Power I/O: +3.3 volt power supply                                                     |

| VUUIA            | 01         | I VVIN | (requires a separate via to power plane)                                              |

| VDD2A            | G2         | PWR    | Power I/O: +3.3 volt power supply                                                     |

|                  | _          |        | (requires a separate via to power plane)                                              |

| VDD3A            | E1         | PWR    | Power I/O: +3.3 volt power supply                                                     |

|                  |            |        | (requires a separate via to power plane)                                              |

| VDD4A            | E4         | PWR    | Power I/O: +3.3 volt power supply                                                     |

|                  |            |        | (requires a separate via to power plane)                                              |

| VSS1A(H)         | H3         | PWR    | <b>Power GND</b> : +3.3 volt power supply (100ma sink capability)                     |

| 1/0044           | 114        |        | (requires a separate via to power plane)                                              |

| VSS1A            | H4         | PWR    | <b>Power GND</b> : +3.3 volt power supply<br>(requires a separate via to power plane) |

| VSS2A            | G3         | PWR    | Power GND: +3.3 volt power supply                                                     |

| VOOZA            | 00         | I WVIX | (requires a separate via to power plane)                                              |

| VSS3A            | E3         | PWR    | Power GND: +3.3 volt power supply                                                     |

|                  | _          |        | (requires a separate via to power plane)                                              |

| VSS4A            | E2         | PWR    | Power GND: +3.3 volt power supply                                                     |

|                  |            |        | (requires a separate via to power plane)                                              |

|                  |            |        | MII Ethernet 1 Interface (External PHY)                                               |

|                  | <b>D</b> 4 | 1/0    | All bi-directional during factory testing                                             |

| MDIO             | P1         | I/O    | Ethernet MII 1 Management Data (4ma with Input and Pull-down)                         |

| MDC              | N1         | OUT    | Ethernet MII 1 Clock Out (4ma with Input and Pull-down)                               |

| TXCLK            | M2         | IN     | Ethernet Transmit Clock (4ma with Input and Pull-down)                                |

| TXEN             | L3         | OUT    | Ethernet Transmit Enable (4ma with Input and Pull-down)                               |