# **DSTni-EX User Guide**

**Section Two**

## **Copyright & Trademark**

© 2003 Lantronix, Inc. All rights reserved.

Lantronix and the Lantronix logo, and combinations thereof are registered trademarks of Lantronix, Inc. DSTni is a registered trademark of Lantronix, Inc. Ethernet is a registered trademark of Xerox Corporation. All other product names, company names, logos or other designations mentioned herein are trademarks of their respective owners.

- ♦ Am186 is a trademark of Advanced Micro Devices, Inc.

- Ethernet is a registered trademark of Xerox Corporation.

- SPI is a trademark of Motorola, Inc.

No part of this guide may be reproduced or transmitted in any form for any purpose other than the purchaser's personal use, without the express written permission of Lantronix, Inc.

#### Lantronix

15353 Barranca Parkway Irvine, CA 92618, USA Phone: 949-453-3990 Fax: 949-453-3995

#### **Technical Support**

Phone: 630-245-1445 Fax: 630-245-1717

#### **Master Distributor**

Grid Connect 1841 Centre Point Circle, Suite 143 Naperville, IL 60563

Phone: 630-245-1445 www.gridconnect.com

Am186 is a trademark of Advanced Micro Devices, Inc. Ethernet is a registered trademark of Xerox Corporation. SPI is a trademark of Motorola, Inc.

| REV | Changes                                     | Released Date |

|-----|---------------------------------------------|---------------|

| Α   | Reformat. Add changes from Design Spec. 1.1 | 3-24-04       |

## **Contents**

| Copyright & Trademark                                               | i  |

|---------------------------------------------------------------------|----|

| About This User Guide                                               | 1  |

| Intended Audience                                                   |    |

| Conventions                                                         | 2  |

| Navigating Online                                                   | 2  |

| Organization                                                        | 3  |

| Microprocessor                                                      | 5  |

| Overview                                                            | 5  |

| Block Diagram                                                       | 5  |

| Theory of Operation                                                 |    |

| Overview                                                            |    |

| CPU Core                                                            | 6  |

| Programming Model                                                   | 8  |

| Instruction Set and Execution Times                                 |    |

| Memory Organization                                                 | 10 |

| Addressing Modes                                                    | 12 |

| Data Types                                                          | 13 |

| Input/Output Space                                                  | 13 |

| Input/Output Space DSTni Peripherals                                | 14 |

| Peripheral Control Block                                            | 14 |

| Setting the PCB Base Location                                       | 15 |

| Direct Memory Access                                                | 15 |

| DMA Transfer Directions                                             | 15 |

| DMA Transfer Process                                                | 16 |

| DMA Operation                                                       | 16 |

| DMA Priority                                                        | 16 |

| Register Summary                                                    | 17 |

| Register Definitions                                                |    |

| PCB Relocation Register                                             |    |

| DSTni Configuration Register                                        |    |

| Reset Configuration Register                                        |    |

| Processor Release Level Register                                    | 22 |

| Auxiliary Configuration Register                                    |    |

| System Configuration Register                                       | 24 |

| DMA Control Registers                                               | 25 |

| DMA Transfer Count Registers                                        | 27 |

| DMA Destination Address High Registers                              | 28 |

| DMA Destination Address Low Registers                               | 29 |

| DMA Source Address High Registers                                   |    |

| DMA Source Address Low Registers                                    | 30 |

| READY Signal and Wait States                                        |    |

| Wait State Generation                                               | 31 |

| Page Chip Select RegisterPCS and MCS Auxiliary Register             | 32 |

| Midran and Marson Chin Colort Dovictor                              | 34 |

| Midrange Memory Chip Select Register                                |    |

| Peripheral Chip Select Register                                     | 3/ |

| Lower Memory Chip Select Register Upper Memory Chip Select Register | 39 |

| · · · · · · · · · · · · · · · · · · ·                               | 40 |

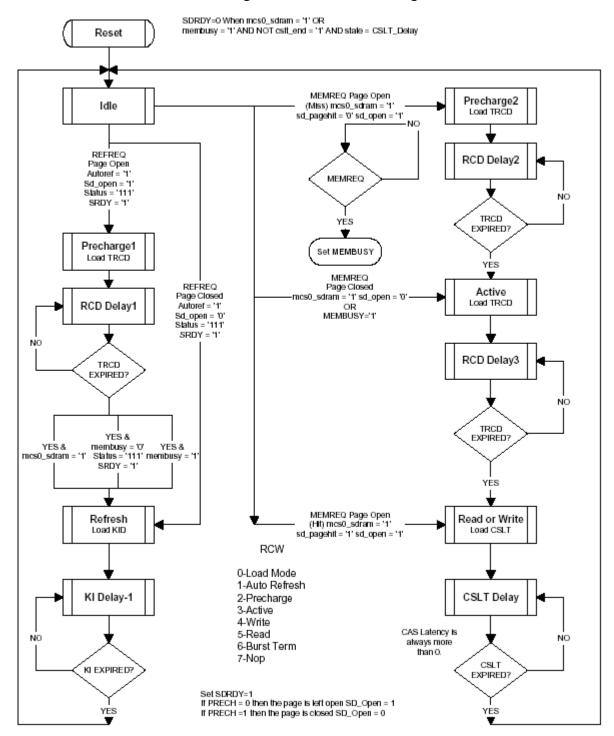

| SDRAM                                                               |    |

| SDRAM Flow Diagram                                                  |    |

| SDRAM Operation                                                     | 45 |

| Initializing SDRAM                                                  | 46 |

| SDRAM Register Summary                                              | 47 |

| SDRAM Register Definitions                                          | 47 |

| SDRAM Refresh Max Count Register                                    | 47 |

| SDRAM Control Register                                              | 49 |

# **List of Figures**

|                    | Figure 0-1. CPU Block Diagram                                                           |    |

|--------------------|-----------------------------------------------------------------------------------------|----|

|                    | Figure 0-2. CPU Core                                                                    |    |

|                    | Figure 0-3. CPU Programming Model                                                       |    |

|                    | Figure 0-4. Status Word Bit Format                                                      |    |

|                    | Figure 0-5. 20-Bit Address Generation                                                   |    |

|                    | Figure 0-6. 24-Bit Address Generation                                                   |    |

|                    | Figure 0-1. SDRAM Flow Diagram                                                          |    |

|                    | Figure 0-2. SDRAM Refresh Diagram                                                       | 48 |

|                    |                                                                                         |    |

|                    |                                                                                         |    |

| <b>List of Tab</b> | loc                                                                                     |    |

| LIST OF TAB        | les                                                                                     |    |

|                    |                                                                                         |    |

|                    | Table 0-1. Status Word Bit Functions                                                    |    |

|                    | Table 0-2. Segment Register Selection Rules                                             |    |

|                    | Table 0-3. CPU Registers After Reset                                                    |    |

|                    | Table 0-4. System Register Summary                                                      |    |

|                    | Table 0-5. DMA Controller Register Summary                                              |    |

|                    | Table 0-6. PCB Relocation Register                                                      |    |

|                    | Table 0-7. PCB Relocation Register Definitions                                          |    |

|                    | Table 0-8. DSTni Configuration Register                                                 | 19 |

|                    | Table 0-9. DSTni Configuration Register Definitions                                     | 20 |

|                    | Table 0-10. Default Reset Values                                                        | 21 |

|                    | Table 0-11. Reset Configuration Register                                                | 22 |

|                    | Table 0-12. Reset Configuration Register Definitions                                    | 22 |

|                    | Table 0-13. Processor Release Level Register                                            |    |

|                    | Table 0-14. Processor Release Level Register Definitions                                | 22 |

|                    | Table 0-15. Auxiliary Configuration Register                                            |    |

|                    | Table 0-16. Auxiliary Configuration Register Definitions                                |    |

|                    | Table 0-17. System Configuration Register                                               |    |

|                    | Table 0-18. System Configuration Register Definitions                                   |    |

|                    | Table 0-19. DMA Control Registers                                                       |    |

|                    | Table 0-20. DMA Control Register Definitions                                            |    |

|                    | Table 0-21. DMA Transfer Count Registers                                                |    |

|                    | Table 0-22. DMA Transfer Count Register Definitions                                     |    |

|                    | Table 0-23. DMA Destination Address High Registers                                      |    |

|                    | Table 0-24. DMA Destination Address High Register Definitions                           |    |

|                    | Table 0-25. DMA Destination Address Low Registers                                       |    |

|                    | Table 0-26. DMA Destination Address Low Register Definitions                            |    |

|                    | Table 0-27. DMA Source Address High Registers                                           |    |

|                    | Table 0-28. DMA Source Address High Register Definitions                                | 30 |

|                    | Table 0-29. DMA Source Address Low Registers                                            |    |

|                    | Table 0-30. DMA Source Address Low Register Definitions                                 |    |

|                    |                                                                                         | 31 |

|                    | Table 0-32. Page Chip Select Register                                                   |    |

|                    | Table 0-33. Page Chip Select Register Definitions                                       |    |

|                    | Table 0-34. Page or Burst Size Values                                                   | 3/ |

|                    | Table 0-34: Fage of Burst Size Values                                                   |    |

|                    | Table 0-35. PCS and MCS Auxiliary Register Definitions                                  |    |

|                    |                                                                                         |    |

|                    | Table 0-37. Block Sizes  Table 0-38. Midrange Memory Chip Select Register (20-Bit Mode) |    |

|                    |                                                                                         |    |

|                    | Table 0-39. Midrange Memory Chip Select Register (24-Bit Mode)                          |    |

|                    | Table 0-40. Midrange Memory Chip Select Register Definitions                            |    |

|                    | Table 0-41. Peripheral Chip Select Register (20-Bit Mode)                               |    |

|                    | Table 0-42. Peripheral Chip Select Register (24-Bit Mode)                               |    |

|                    | Table 0-43. Peripheral Chip Select Register Definitions                                 |    |

|                    | Table 0-44. PCS Address Ranges                                                          | 38 |

| Table 0-45. Wait State Generation                           | 38 |

|-------------------------------------------------------------|----|

| Table 0-46. Lower Memory Chip Select Register (20-Bit Mode) | 39 |

| Table 0-47. Lower Memory Chip Select Register (24-Bit Mode) |    |

| Table 0-48. Lower Memory Chip Select Register Definitions   | 39 |

| Table 0-49. Upper Memory Chip Select Register (20-Bit Mode) | 40 |

| Table 0-50. Upper Memory Chip Select Register (24-Bit Mode) | 40 |

| Table 0-51. Upper Memory Chip Select Register Definitions   |    |

| Table 0-52. Example of Upper Memory Chip Select Settings    | 41 |

| Table 0-1. SDRAM Operation (16/64/128 MB)                   | 45 |

| Table 0-2. Addresses and Corresponding CAS Latencies        | 46 |

| Table 0-3. SDRAM Registers                                  | 47 |

| Table 0-4. SDRAM Refresh Max Count Register                 | 47 |

| Table 0-5. SDRAM Refresh Max Count Register Definitions     |    |

| Table 0-6. SDRAM Control Register                           |    |

| Table 0-7. SDRAM Control Register Definitions               |    |

## **About This User Guide**

This User Guide describes the technical features and programming interfaces of the Lantronix DSTni-EX chip (hereafter referred to as "DSTni").

DSTni is an Application Specific Integrated Circuit (ASIC)-based single-chip solution (SCS) that integrates the leading-edge functionalities needed to develop low-cost, high-performance device server products. On a single chip, the DSTni integrates an x186 microprocessor, 16K-byte ROM, 256K-byte SRAM, programmable input/output (I/O), and serial, Ethernet, and Universal Serial Bus (USB) connectivity — key ingredients for device- server solutions. Although DSTni embeds multiple functions onto a single chip, it can be easily customized, based on the comprehensive feature set designed into the chip.

Providing a complete device server solution on a single chip enables system designers to build affordable, full-function solutions that provide the highest level of performance in both processing power and peripheral systems, while reducing the number of total system components. The advantages gained from this synergy include:

- Simplifying system design and increased reliability.

- Minimizing marketing and administration costs by eliminating the need to source products from multiple vendors.

- Eliminating the compatibility and reliability problems that occur when combining separate subsystems.

- Dramatically reducing implementation costs.

- Increasing performance and functionality, while maintaining quality and cost effectiveness.

- Streamlining development by reducing programming effort and debugging time.

- Enabling solution providers to bring their products to market faster.

These advantages make DSTni the ideal solution for designs requiring x86 compatibility; increased performance; serial, programmable I/O, Ethernet, and USB communications; and a glueless bus interface.

## **Intended Audience**

This User Guide is intended for use by hardware and software engineers, programmers, and designers who understand the basic operating principles of microprocessors and their systems and are considering designing systems that utilize DSTni.

### **Conventions**

This User Guide uses the following conventions to alert you to information of special interest.

The symbols # and n are used throughout this Guide to denote active LOW signals.

**Notes:** Notes are information requiring attention.

## **Navigating Online**

The electronic Portable Document Format (PDF) version of this User Guide contains <u>hyperlinks</u>. Clicking one of these hyper links moves you to that location in this User Guide. The PDF file was created with Bookmarks and active links for the Table of Contents, Tables, Figures and cross-references.

## **Organization**

This User Guide contains information essential for system architects and design engineers. The information in this User Guide is organized into the following chapters and appendixes.

♦ Section 1: Introduction

Describes the DSTni architecture, design benefits, theory of operations, ball assignments, packaging, and electrical specifications. This chapter includes a DSTni block diagram.

♦ Section 2: Microprocessor

Describes the DSTni microprocessor and its control registers.

♦ Section 2: SDRAM

Describes the DSTni SDRAM and the registers associated with it.

♦ Section 3: Serial Ports

Describes the DSTni serial ports and the registers associated with them.

Section 3: Programmable Input/Output

Describes DSTni's Programmable Input/ Output (PIO) functions and the registers associated with them.

♦ Section 3: Timers

Describes the DSTni timers.

Section 4: Ethernet Controllers

Describes the DSTni Ethernet controllers.

Section 4: Ethernet PHY

Describes the DSTni Ethernet physical layer core.

♦ Section 5: SPI Controller

Describes the DSTni Serial Peripheral Interface (SPI) controller.

Section 5: I2C Controller

Describes the DSTni I<sup>2</sup>C controller.

♦ <u>Section 5: USB Controller</u>

Describes the DSTni USB controller.

♦ Section 5: CAN Controllers

Describes the DSTni Controller Area Network (CAN) bus controllers.

♦ Section 6: Interrupt Controller

Describes the DSTni interrupt controller.

♦ Section 6: Miscellaneous Registers

Describes DSTni registers not covered in other chapters of this Guide.

- Section 6: Debugging In-circuit Emulator (Delce)

- ♦ Section 6: Packaging and Electrical

Describes DSTni's packaging and electrical characteristics.

♦ *Section 6: Applications*

Describes DSTni's packaging and electrical characteristics.

♦ Section 6: Instruction Clocks

Describes the DSTni instruction clocks.

- ♦ Section 6: DSTni Sample Code

- ♦ Section 6: Baud Rate Calculations

Provides baud rate calculation tables.

# **Microprocessor**

## **Overview**

The DSTni chip is based on the x86 architecture. This chapter describes the DSTni microprocessor. Topics include:

- Block Diagram on page 5

- Theory of Operation on page 6

- Register Summary on page 17

- Register Definitions on page 18

## **Block Diagram**

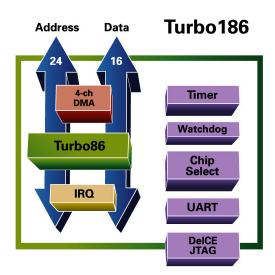

Figure 0-1. CPU Block Diagram

## **Theory of Operation**

#### Overview

The embedded CPU is a performance-enhanced implementation of the industry-standard 80186 microprocessor. The CPU has been rearchitected from the ground up using the latest design techniques to produce an efficient, high clock-rate CPU core that is greatly improved over standard component implementations. The CPU greatly leverages many years of experience in providing 8086 software compatibility in dozens of SoC designs. All of the 8086 compatibility tests accumulated to establish the compatibility of the CPU core have been used to establish the compatibility of CPU.

The CPU provides approximately 2.5 times the performance of the AMD or Intel 80186 at the same clock frequency. Low-power applications that do not need this increased performance can run at half the clock frequency and still obtain greater throughput. The performance advantage of the CPU is magnified to over five times with its ability to operate at two to three times the clock frequency of standard components. The result is a processor core that exceeds the performance of the 386SX in real mode applications.

The CPU integrates the 186 set of versatile peripherals with compatibility with the Intel 80C186 or AMD Am186ES. The CPU has been enhanced with all of the 80186 instruction-set enhancements to provide 100% software compatibility with the industry-standard 80186.

On-chip peripherals are always accessed as 16-bit bus cycles.

#### **CPU Core**

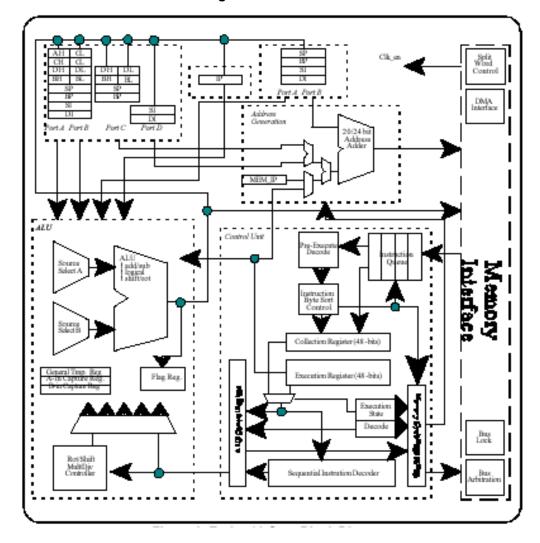

The CPU core implements an 8086 microprocessor, and includes the 10 additional 80186 instructions. This allows the CPU to be fully software compatible with 8086 and 80186 family of processors. Figure 0-2 shows a block diagram of the CPU core.

Figure 0-2. CPU Core

## **Programming Model**

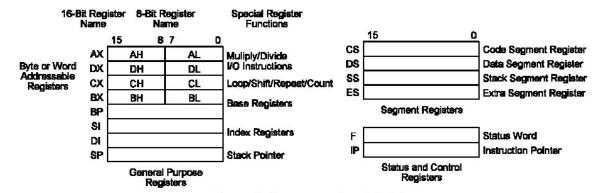

Figure 0-3 shows the CPU programming model.

Figure 0-3. CPU Programming Model

To maintain full program compatibility with the 8086 and the 80186, all registers have been fully implemented.

#### **General Purpose Register File**

The general purpose register file consists of eight 16-bit registers, as shown in Figure 0-3. Any of these registers can be used as general purpose registers. Four of these 16-bit registers AX, BX, CX, and DX can also be accessed as a pair of 8-bit registers. When accessing these registers as byte registers they are referred to as AL, AH, BL, BH, CL, CH, DL, and DH. Some of the general purpose registers also have dedicated functions with certain instructions as noted in Figure 0-3. The AX and DX registers are used during multiply, divide, and I/O instructions. The CX register is used during instructions that have a repeat count for example Loop, shift, and rep. BX and BP can be used as base pointers used during effective address calculations. SI and DI can be used as index registers during effective address calculations.

#### Segment Register File

The segment register file consists of four 16-bit registers, as shown in Figure 0-3. The segment register serve a special function, they select the active segment that is used for code, stack, and data. The CPU core has implicit rules coded into each instruction regarding segment selection, as shown in **Table 2**.

#### Status and Instruction Pointer Registers

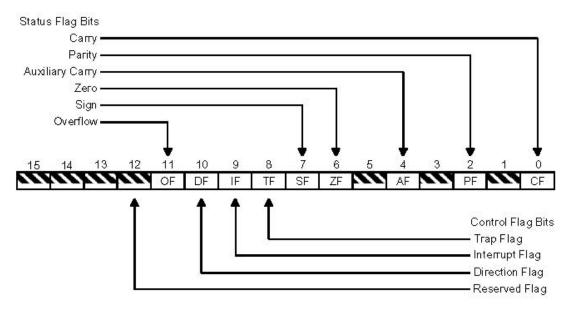

The status word and instruction pointer registers maintain CPU processor state information. The instruction pointer (IP) contains an offset into the current code segment where the next instruction to be executed resides. The status word register contains status and control flags. The format of the status register is shown in Figure 0-4. Arithmetic and logical instructions will affect the status flags (bits 0, 2, 4, 6, 7, and 11) based on the result of an instruction. While the control flags (bits [8], [9], and [10]) determine certain processing control information. The status word bit functions are shown in Figure 0-1 and defined in Table 0-1.

Figure 0-4. Status Word Bit Format

**Table 0-1. Status Word Bit Functions**

| Name | Function                                                                                                                                   |

|------|--------------------------------------------------------------------------------------------------------------------------------------------|

| CF   | Carry Flag Set if a high-order bit carry or borrow occurred. Otherwise, it is cleared.                                                     |

| PF   | Parity Flag Set of the lower 8 bits of a result contain an even number of '1's. Otherwise, it is cleared.                                  |

| AF   | Auxiliary Carry Set if a carry from or borrow to the low-order four bits of the General Purpose register AL. Otherwise, it is cleared.     |

| ZF   | Zero Flag Set if the result is '0'. Otherwise, it is cleared.                                                                              |

| SF   | Sign Flag Set equal to the high-order bit of a result ('0' is positive, '1' if negative).                                                  |

| TF   | Single Step Flag If set, a single-step interrupt occurs after the next instruction executes. TF is cleared by the single-step instruction. |

| IF   | Interrupt Enable Flag Setting this bit enables maskable interrupt.                                                                         |

| DF   | Direction Flag Used during single instructions to determine auto-decrement (DF=1) or auto increment (DF=0) of index value.                 |

| OF   | Overflow Flag Set if the signed result cannot be expressed by the number of bits in the resultant operand. Otherwise, it is cleared.       |

## **Instruction Set and Execution Times**

This section lists all CPU instructions and gives execution times in clock cycles. The 8086/80186 instruction set is fully documented in a variety of publicly available documents and is not described in detail here.

Note: The cycle times represent the number of clock periods an instruction takes to execute after reaching the CPU execution unit. Additional delays may be present in the instruction stream due to the singular bus architecture used by x86. These delays will be deterministic for any given instruction stream but are difficult to quantify in simple terms since they result from the interaction of multiple instructions. The CPU minimizes these delays (often zero) through the use of pipelining and an instruction buffer queue.

## **Memory Organization**

The CPU can address 1MB of physical memory in compatible mode, or 16Mb of physical memory in 24-bit enhanced mode. In either of these modes memory organization is similar.

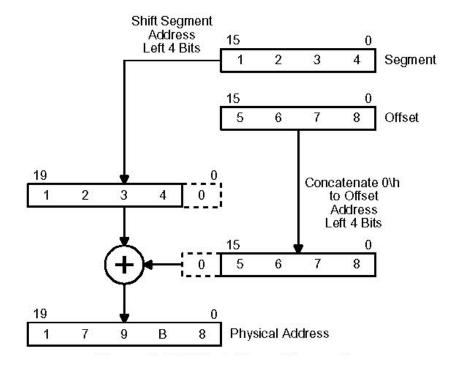

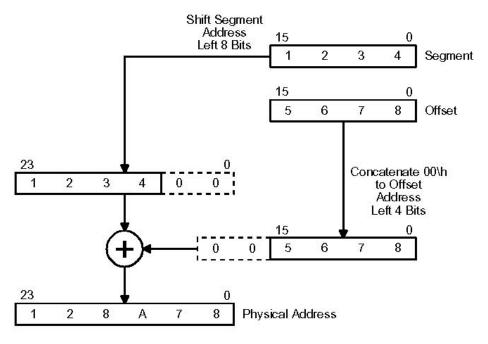

Memory is organized in sets of segments. Each segment is a linear contiguous sequence of up to 64K 8-bit bytes. To address memory, two 16-bit pointers must be added together. In compatible mode, the 20-bit address is generated by shifting a segment value left by 4-bits and adding it to a 16-bit offset or effective address (see Figure 0-5). In enhanced mode, the 24-bit address is generated by shifting a segment value left by 8-bits and adding it to a 16-bit offset or effective address (see Figure 0-6).

In either compatible or enhanced mode all instructions that address operands in memory must specify a segment register and the 16-bit offset value. Segment registers used for physical address generation are implied by the addressing mode used (see Table 0-2). These rules follow the way programs are written as independent modules that require areas for code, data, stack, and external data areas.

Special segment override instruction prefixes allow the implicit segment register selection rules to be overridden for special cases.

**Table 0-2. Segment Register Selection Rules**

| Memory Reference       | Segment<br>Register Used | Implicit Segment Selection Rule                                                  |

|------------------------|--------------------------|----------------------------------------------------------------------------------|

| Instructions           | Code (CS)                | Instruction prefetch and immediate data                                          |

| Local Data             | Data (DS)                | All other data references                                                        |

| Stack                  | Stack (SS)               | All stack pushes and pops; any memory references that use BP as a base register. |

| External Data (Global) | Extra (ES)               | All string instruction references that use the DI register                       |

|                        |                          | as an index.                                                                     |

Figure 0-5. 20-Bit Address Generation

Figure 0-6. 24-Bit Address Generation

### **Addressing Modes**

The CPU supports all the original 8086 addressing modes. There are eight categories of addressing mode to specify operands. Two addressing modes are provided that operate on register or immediate data:

- Register Operand Mode: The operand is located in one of the 8 or 16-bit registers.

- Immediate Operand Mode: The operand is located in the instruction.

Six modes are provided to specify the location of an operand in a memory segment. A memory operand address consists of two 16-bit components: a segment and an offset. The segment base is supplied by a 16-bit segment register either implicitly chosen by the addressing mode or explicitly chosen by a segment override prefix (see Table 0-2 on page 10). The offset, which is also called the effective address, is calculated by summing any combination of the following three address elements:

- The displacement, which is an 8 or 16-bit immediate value contained in the instruction.

- The base, which is either the BX or BP registers.

- The index, which is either the SI or DI registers.

All effective address calculations are done as 16-bit additions any carry out is ignored. All 8-bit displacements are sign extended to 16-bits. Combinations of these three address elements define the six memory addressing modes for the CPU. These addressing modes are as follows:

- Direct Mode: The operand's offset is contained in the instruction as an 8- or 16bit displacement element.

- Register Indirect Mode: The operand's offset is in one of the SI, DI, BX, or BP registers.

- Based Mode: The operand's offset is the sum of an 8 or 16-bit displacement and the contents of a base register (BX or BP).

- Indexed Mode: The operand's offset is the sum of an 8 or 16-bit displacement and the contents of an index register (SI or DI).

- Based Indexed Mode: The operand's offset is the sum of the contents of a base register (BX or BP) and an index register (SI or DI).

- Based Index Mode with Displacement: The operand's offset is the sum of a base register's contents, an index register's contents, and an 8 or 16-bit displacement.

### **Data Types**

The CPU supports the following data types:

Integer: A signed binary numeric value contained in an 8-bit byte or 16-bit

word. All operations assume a two's complement representation.

Ordinal: An unsigned binary numeric value contained in a 8-bit byte or a 16-

bit word.

**Pointer:** These are 16 or 32-bit quantities. Pointers can be composed of a

single 16-bit offset or a 16-bit segment base and 16-bit offset.

**String:** A contiguous sequence of bytes of word. A string maybe 1 to 64

Kbytes in length.

**ASCII:** A byte representation of the alphanumeric and control characters

using the ASCII standard.

**BCD:** A byte representation of the decimal digits 0-9. Also referred to as

an unpacked BCD representation.

Packed BCD: A byte representation of two decimal digits (0-9). One digit is stored

in the lower nibble (bits 3-0), and the second in the upper nibble

(bits [7] through [4]).

## **Input/Output Space**

The CPU can address a maximum of 64K bytes or 32K words of I/O. The IN and OUT instructions are used to transfer data between the AL register for byte I/O, and the AX register for word I/O. Accesses to and from I/O space are not segmented. To access a port, the BIU places the port address (0-64K) specified by the I/O instruction on address bits [15] through [0]. The address bits above bit [15] are always zero for I/O cycles.

Note: I/O port addresses 00F8\h through 00FF\h are reserved.

The CPU can be initialized to a defined state by asserting the RSTIN# input LOW. This causes all processor activity to terminate, the processor remains in an idle state while RSTIN# input low. When the RSTIN# input finally returns HIGH, certain internal registers are initialize,d as shown in Table 0-3. Program execution will begin at one of two addresses depending if operating in compatible or enhanced mode. In compatible mode program execution begins at 0FFFF0\h [CS:FFFF IP:0000], enhanced 24-bit mode program execution begins at FFFFE0\h [CS:FFFF;IP:00E0].

Table 0-3. CPU Registers After Reset

| Register Name          | Value After Reset              |

|------------------------|--------------------------------|

| Status Word            | F000\h                         |

| Instruction Pointer    | 0000\h (00E0\h in 24-bit mode) |

| Code Segment Register  | FFFF\h                         |

| Data Segment Register  | 0000\h                         |

| Extra Segment Register | 0000\h                         |

| Stack Segment Register | 0000\h                         |

### **DSTni Peripherals**

DSTni is software compatible with popular 80186 designs. It is similar to an AMD AM186ES. A few minor functions, such as the refresh controller and certain control bits related to the design of the original 80C186XL bus controller, have been omitted from these versions. Where discrepancies exist between the original specifications from the manufacturers and this specification, the data in this specification takes precedent.

The following peripherals are included in all of the CPU peripheral collections.

- Chip select-and-ready control logic

- 4-channel DMA controller

- ♦ Three programmable 16-bit timers

- Interrupt controller (Master Mode Only)

Each peripheral has been designed from the ground up to provide a fully synchronous operation with the CPU core. All the peripherals support zero-wait state accesses and work with the single cycle CPU through an internal bridge.

**Note:** All internal peripherals should only be written with 16-bit writes. Byte writes are not supported to the CPU peripherals and may cause unpredictable behavior. No power-save features are available in the CPU. CPU clock speed may be reduced to save power.

### **Peripheral Control Block**

All integrated DSTni peripherals are controlled by sets of 16-bit registers contained within a 256-byte integrated Peripheral Control Block (PCB). The peripheral control registers are physically located in the peripheral devices they control, but are addressed as a single 256-byte block. The PCB encompasses 256 contiguous bytes and can reside on any 256-byte boundary of memory or input/output (I/O) space. The PCB Relocation register, which is also located within the PCB, controls the PCB location.

#### **Peripheral Control Registers**

Each of the integrated peripheral's registers is located at a fixed offset above the programmed base location of the PCB. These registers are described in the chapters that cover the associated peripheral.

#### **PCB** Relocation Register

In addition to control registers for the integrated peripherals, the PCB contains a PCB Relocation register. The Relocation register is located at a fixed offset within the PCB. If the PCB moves, the Relocation register also moves.

The PCB Relocation register allows the PCB to relocate to any 256-byte boundary within memory or I/O space. In 24-bit mode, the PCB can only reside in the lower 1 MB. The Memory I/O bit (bit [12] of the Relocation register) selects either memory or I/O space, and bits [19:8] specify the starting (base) address of the PCB.

For information about setting the base location and restrictions on the PCB location, see Setting the PCB Base Location on page 15.

#### **Reserved Locations**

Some locations within the PCB are not assigned to any peripheral. Unused locations are reserved and marked with "///" in the register tables under Register Definitions on page 18. Reading from these locations yields an undefined result. If reserved register locations are written (for example, during a block MOV instruction), they should be set to 0h.

#### **Accessing the PCB**

Like all integrated peripherals, the PCB is always accessed 16 bits at a time.

## **Bus Cycles**

The microprocessor runs an external bus cycle for any memory or I/O cycle accessing a location within the PCB. Address, data and control information are driven on the external pins as with an ordinary bus cycle. Information returned by an external device is ignored, even if the access does not correspond to the location of an integrated peripheral control register.

#### Writing the PCB Relocation Register

When mapping the PCB to another location, program the Relocation register with a word write (i.e., OUT DX, AX).

### **Setting the PCB Base Location**

Upon reset, the PCB Relocation register contains the value 00FFh. Writing the PCB Relocation register lets you change this location.

For example, to relocate the PCB to the memory range 10000-100FFh, program the PCB Relocation register with the value 1100h. Since the Relocation register is part of the PCB, it relocates to word 10000h plus its fixed offset.

## **Direct Memory Access**

In many applications, large blocks of data must transfer between memory and I/O space. A disk drive, for example, reads and writes data in blocks that can be thousands of bytes long. If the microprocessor had to handle each byte of the transfer, the main tasks would suffer a severe performance penalty. Even if the data transfers was interrupt-driven, the overhead for transferring control to the interrupt handler would still decrease system throughput.

DMA enables data to transfer between memory and peripherals without requiring microprocessor intervention. Data transfers can occur between memory and I/O spaces or within the same (see DMA Transfer Process on page 16). DSTni provides four high-speed DMA channels. All four DMA channels are functionally identical and can directly connect to the asynchronous serial ports.

Each channel accepts a DMA request from one of four sources:

- The channel request pin (DRQ3–DRQ0)

- Timer 2

- A serial port

- Svstem software

Furthermore, the channels can be programmed with different priorities in the event of a simultaneous DMA request or if there is a need to interrupt transfers on one of the other channels.

Either bytes or words can be transferred to or from even or odd addresses on DSTni. However, DSTni does not support word DMA transfers to or from memory configured for 8-bit accesses. Only two bus cycles are needed for each data transfer.

#### **DMA Transfer Directions**

The source and destination addresses for a DMA transfer are programmable and can be in either memory or I/O space. DMA transfers can be programmed for any of the following four directions:

- From memory space to I/O space

- From I/O space to memory space

- From memory space to memory space

- From I/O space to I/O space

DMA transfers can access the PCB.

#### **DMA Transfer Process**

The following sequence describes the DMA process:

- 1. A peripheral sends a request for a transfer to the DMA controller.

- The DMA controller signals the microprocessor that it needs control of the system bus.

- 3. The microprocessor releases control of the bus and the DMA controller performs the transfer. In many cases, the microprocessor releases the bus and continues to execute instructions from the prefetch queue.

Every DMA transfer consists of two distinct bus cycles: a fetch and a deposit.

- During the fetch cycle, the byte or word is read from the data source and placed in an internal temporary storage register.

- During the deposit cycle, the data in the temporary storage register writes to the destination.

The fetch and deposit bus cycles are indivisible and cannot be separated by a bus hold request, a refresh request, or another DMA request. If the DMA transfers are relatively infrequent, the DMA transfer is transparent to the microprocessor and there is no degradation of software performance.

### **DMA Operation**

Each channel has the following 16-bit registers in the PCB that define specific channel operations:

- Two DMA Address High registers one for source and one for destination.

- Two DMA Address Low registers one for source and one for destination.

- ◆ A DMA Transfer Count register which specifies the number of DMA transfers to be performed. Up to 64K of byte or word transfers can be performed with automatic termination.

- A DMA Channel Control register which determines the operating mode for the particular DMA channel.

All registers can be modified during any DMA activity. Any changes made to the DMA registers are reflected immediately in DMA operation. For more information, see Register Summary on page 17.

## **DMA Priority**

You can program the DMA channels so that one channel always has priority over the others, or so they alternate cycles when all four have DMA requests pending. DMA cycles always have priority over internal microprocessor cycles, except between locked memory accesses or word accesses to odd memory locations. However, an external bus hold takes priority over an internal DMA cycle.

Because an interrupt request cannot suspend a DMA operation, and because the microprocessor cannot access memory during a DMA cycle, interrupt latency time suffers during sequences of continuous DMA cycles. An NMI request, however, causes all internal DMA activity to halt. This allows the microprocessor to respond quickly to the NMI request.

# **Register Summary**

Table 0-4. System Register Summary

| Hex Offset | Mnemonic | Register Description                         | Page |

|------------|----------|----------------------------------------------|------|

| FE         | RELREG   | Peripheral Control Block Relocation register | 18   |

| FC         | ///      | ///                                          | ///  |

| FA         | ///      | ///                                          | ///  |

| F8         | DCR      | DSTni Configuration register                 | 19   |

| F6         | RCR      | Reset Configuration register                 | 22   |

| F4         | PRL      | Processor Release Level register             | 22   |

| F2         | AUXCON   | Auxiliary Configuration register             | 23   |

| F0         | SYSCON   | System Configuration register                | 24   |

Table 0-5. DMA Controller Register Summary

| Hex Offset | Mnemonic | Register Description                   | Page |

|------------|----------|----------------------------------------|------|

| DMA0 = CA  | D0CON    | DMA Control registers                  | 25   |

| DMA1 = DA  | D1CON    |                                        |      |

| DMA2 = 9A  | D2CON    |                                        |      |

| DMA3 = BA  | D3CON    |                                        |      |

| DMA0 = C8  | D0TC     | DMA Transfer Count registers           | 27   |

| DMA1 = D8  | D1TC     |                                        |      |

| DMA2 = 98  | D2TC     |                                        |      |

| DMA3 = B8  | D3TC     |                                        |      |

| DMA0 = C6  | D0DTSH   | DMA Destination Address High registers | 28   |

| DMA1 = D6  | D1DTSH   |                                        |      |

| DMA2 = 96  | D2DTSH   |                                        |      |

| DMA3 = B6  | D3DTSH   |                                        |      |

| DMA0 = C4  | D0DSTL   | DMA Destination Address Low registers  | 29   |

| DMA1 = D4  | D1DSTL   |                                        |      |

| DMA2 = 94  | D2DSTL   |                                        |      |

| DMA3 = B4  | D3DSTL   |                                        |      |

| DMA0 = C2  | D0SRCH   | DMA Source Address High registers      | 29   |

| DMA1 = D2  | D1SRCH   |                                        |      |

| DMA2 = 92  | D2SRCH   |                                        |      |

| DMA3 = B2  | D3SRCH   |                                        |      |

| DMA0 = C0  | D0SRCL   | DMA Source Address Low registers       | 30   |

| DMA1 = D0  | D1SRCL   |                                        |      |

| DMA2 = 90  | D2SRCL   |                                        |      |

| DMA3 = B0  | D3SRCL   |                                        |      |

## **Register Definitions**

The following sections provide the microprocessor register definitions. In these sections, the initialization value shown is the register's initialization value at reset.

## **PCB Relocation Register**

The PCB Relocation register is a 16-bit register that maps the PCB into either memory or I/O space. This register provides the upper 12 bits of the control block's base address. The control block is effectively an internal chip select range.

Other chip selects can overlap the control block if they are programmed to zero wait states and ignore external ready. If the control register block maps into I/O space, the upper four bits of the base address must be programmed as 0000b, since I/O addresses are only 16 bits wide. At reset, this register is set to 00FFh, which maps the control block to start at FF00h in I/O space.

Table 0-6. PCB Relocation Register

| BIT    | 15  | 14  | 13  | 12   | 11 | 10                           | 9  | 8  | 7  | 6  | 5  | 4  | 3  | 2  | 1  | 0  |

|--------|-----|-----|-----|------|----|------------------------------|----|----|----|----|----|----|----|----|----|----|

| OFFSET | FEh |     |     |      |    |                              |    |    |    |    |    |    |    |    |    |    |

| FIELD  | /// | /// | /// | M/IO |    | Relocation Address RA [19:8] |    |    |    |    |    |    |    |    |    |    |

| RESET  | 0   | 0   | 0   | 0    | 0  | 0                            | 0  | 0  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  |

| RW     | RW  | RW  | RW  | RW   | RW | RW                           | RW | RW | RW | RW | RW | RW | RW | RW | RW | RW |

**Table 0-7. PCB Relocation Register Definitions**

| Bits  | Field Name                   | Description                                                       |

|-------|------------------------------|-------------------------------------------------------------------|

| 15:13 | ///                          | Reserved                                                          |

| 12    | M/IO                         | PCB Location 0 = PCB is in I/O space. 1 = PCB is in memory space. |

| 11:0  | Relocation Address RA [19:8] | Defines the 256-byte boundary where the PCB resides.              |

## **DSTni Configuration Register**

The DSTni Configuration register is a Read/Write register that is reset using the values on address lines 22 down to 8 as DSTni exits reset.

This register may be written to by the CPU. However exercise caution because these values can cause the CPU to enter invalid modes.

**Note:** The reset value of these bits is determined by internal pull-up/down resistors. These values may be overridden by the presence or absence of external pull-up/down resistors. If an external resistor is not applied, each bit has a default value as described by Table 0-10.

The DCR allows hardware design-time configuration choices to be made when designing a new product around DSTni-EX. It is possible but not common for software to modify the contents of this register.

SPIEN selects between SPI or Serial Port 3 on 4 of the 16 PIO pins. When SPI is enabled, Serial Port 3 cannot be used.

The bit values in the DSTni Configuration register correspond to the address bus as the ASIC is reset. The values at the completion of the reset can be modified by applying the proper pull up or pull-down resistors externally to override the default internal resistors (see *Table 0-10*). DCR pins that are not assigned to hardware functions are used to configure the behavior of the on-chip boot ROM when it is enable (BROMEN = 1). Refer to the DSTni-EX Bootstrap User Guide for information about other uses of DCR.

BIT 15 14 13 10 9 8 OFFSET F8h FIELD WDOGEN BROMEN ADDR24 N E N /// /// /// /// /// /// /// /// /// /// /// CSBE SPI RESET 0 RW R RW RW RW RW R R W

Table 0-8. DSTni Configuration Register

Table 0-9. DSTni Configuration Register Definitions

| Bits | Field Name | Description                                                                                                                                                                                                                                                                                                                                         |

|------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15   | ///        | This bit value cannot be changed.                                                                                                                                                                                                                                                                                                                   |

| 14:0 | Data       |                                                                                                                                                                                                                                                                                                                                                     |

| 14   | BROMEN     | Boot ROM Enable  1 = enable the internal Boot ROM.  0 = disable the internal Boot ROM.  The external upper chip select is accessed when the Boot ROM is disabled. The internal Boot ROM always has zero wait states. This bit defaults to 1 with an internal pull-up resistor.  Placing an external pull-down resistor on A22 resets this bit to 0. |

| 13   | ADDR24     | Address 24 Mode  1= enable the CPU to execute in a 24 bit address mode with 16 megabytes of address space.  0 = the CPU executes in real mode x86 1 Megabyte of address space.  This bit defaults to 1 with an internal pull-up resistor.  Placing an external pull-down resistor on A21 resets this bit to 0.                                      |

| 12   | WDOGEN     | Watch Dog Enable  1 = enable the internal watchdog on reset.  0 = disable the watchdog on reset. This can be useful for testing and debugging.  This bit defaults to a 1 with an internal pull-up resistor.  Placing an external pull-down resistor on A20 resets this bit to 0.                                                                    |

| 10   | SPIEN      | SPI Enable  1 = enable the SPI controller on serial port 3.  0 = SPI controller is not connected to the I/O.  This bit defaults to 0 with an internal pull-down resistor.  Placing an external pull-up resistor on A18 resets this bit to reset to 1.                                                                                               |

| 4    | CSBE       | Chip Select Byte Enable  1 = enable WRH_n and WRL_n to connect to byte write enable control signals.  0 = enable byte control signals. This is typical for x16 external static memory devices. This bit defaults to 1 with an internal pull-up resistor.  Placing an external pull-down resistor on A12 resets this bit to 0.                       |

**Table 0-10. Default Reset Values**

| Data    | ADR Pin | Default | Value          | External Connection          | 0 =              |

|---------|---------|---------|----------------|------------------------------|------------------|

| Data 15 |         | 0       | Reserved       | Always zero                  |                  |

| Data 14 | 22      | 1       | BROMEN         | Address Bit 22 (pulled up)   | disabled         |

| Data 13 | 21      | 1       | ADDR24         | Address Bit 21 (pulled up)   | 20-bit           |

| Data 12 | 20      | 1       | WDOGEN         | Address Bit 20 (pulled up)   | disabled         |

| Data 11 | 19      | 0       | SPIBOOT        | Address Bit 19 (pulled down) | disabled         |

| Data 10 | 18      | 0       | SPIEN          | Address Bit 18 (pulled down) | Ser3 uses pins   |

| Data 9  | 17      | 0       | ETHBOOT        | Address Bit 17 (pulled down) | disabled         |

| Data 8  | 16      | 0       | ETHCHAN        | Address Bit 16 (pulled down) | Use chan 0       |

| Data 7  | 15      | 1       | LEDENC         | Address Bit 15 (pulled up)   | 4 mono<br>LEDs   |

| Data 6  | 14      | 1       | PARBOOT        | Address Bit 14 (pulled up)   | Disabled         |

| Data 5  | 13      | 1       | PHYBYPASS      | Address Bit 13 (pulled up)   | Set to<br>10Mbps |

| Data 4  | 12      | 1       | CSBE<br>CSMODE | Address Bit 12 (pulled up)   | Use<br>UCE/LCE   |

| Data 3  | 11      | 0       | SERBOOT        | Address Bit 11 (pulled down) | Disabled         |

| Data 2  | 10      | 0       | SERCHAN        | Address Bit 10 (pulled down) | SP0              |

| Data 1  | 9       | 0       | SERSPEED       | Address Bit 9 (pulled down)  | 57600<br>baud    |

| Data 0  | 8       | 0       | DEBUG          | Address Bit 8 (pulled down)  | disabled         |

## **Reset Configuration Register**

The Reset Configuration register is a Read Only register that latches system-configuration information presented to the microprocessor on the data bus when exiting reset. The interpretation of this information is system-specific. The microprocessor does not impose any predetermined interpretation; it simply acts as a conduit for communicating the information to software.

**Note:** This register resets to a default of all '0's unless pull-up resistors are placed on the external data bus.

**Table 0-11. Reset Configuration Register**

| BIT    | 15 | 14   | 13 | 12 | 11 | 10 | 9 | 8   | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|--------|----|------|----|----|----|----|---|-----|---|---|---|---|---|---|---|---|

| OFFSET |    |      |    |    |    |    |   | F6h | 1 |   |   |   |   |   |   |   |

| FIELD  |    | Data |    |    |    |    |   |     |   |   |   |   |   |   |   |   |

| RESET  | _  | _    | _  | _  | _  | _  | _ | _   | — | _ | _ | _ | _ | _ | _ |   |

| RW     | R  | R    | R  | R  | R  | R  | R | R   | R | R | R | R | R | R | R | R |

Table 0-12. Reset Configuration Register Definitions

| Bits | Field Name | Description                                                                                                                                                                                                                                                                                       |

|------|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15:0 | Data       | A value that corresponds to the data bus as it exits reset. The software uses this value as dictated by the application. The bus is pulled-down by internal resistors. Pull-up resistors placed externally on the data bus can present a 1 value in the corresponding data bit for this register. |

## **Processor Release Level Register**

The Processor Release Level register is a Read Only register that specifies the microprocessor version and type.

Table 0-13. Processor Release Level Register

| BIT    | 15 | 14  | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6    | 5    | 4 | 3        | 2 | 1 | 0 |  |

|--------|----|-----|----|----|----|----|---|---|---|------|------|---|----------|---|---|---|--|

| OFFSET |    | F4h |    |    |    |    |   |   |   |      |      |   |          |   |   |   |  |

| FIELD  |    |     |    | PR | L  |    |   |   |   | OPTI | ONID |   | CPU TYPE |   |   |   |  |

| RESET  | _  | _   | _  | _  | _  | _  | _ |   | 0 | 0    | 0    | 0 | _        |   |   | _ |  |

| RW     | R  | R   | R  | R  | R  | R  | R | R | R | R    | R    | R | R        | R | R | R |  |

Table 0-14. Processor Release Level Register Definitions

| Bits | Field    | Description                                                                |

|------|----------|----------------------------------------------------------------------------|

|      | Name     |                                                                            |

| 15:8 | PRL      | Processor Release Level                                                    |

|      |          | A = 01h, B=02h, etc.                                                       |

| 7:4  | OPTIONID | OPTIONID                                                                   |

|      |          | Indicates the options included in DSTni. These bits also correspond to the |

|      |          | DEVICE_ID in the boundary scan.                                            |

|      |          | DSTni = 0000.                                                              |

| 3:0  | CPU TYPE | Type of CPU                                                                |

|      |          | 0h = AMD, 1h = DSTni-EX, 2h = DSTni-LX                                     |

# **Auxiliary Configuration Register**

The Auxiliary Configuration register configures the asynchronous serial port flow-control signals. It also configures the data bus width for memory and I/O accesses. For more information, refer to the Serial Port theory of operation.

**Table 0-15. Auxiliary Configuration Register**

| BIT    | 15  | 14 | 13 | 12 | 11 | 10    | 9    | 8     | 7    | 6     | 5    | 4     | 3    | 2    | 1    | 0     |

|--------|-----|----|----|----|----|-------|------|-------|------|-------|------|-------|------|------|------|-------|

| OFFSET | F2h |    |    |    |    |       |      |       |      |       |      |       |      |      |      |       |

| FIELD  | /// |    |    |    |    | ENRX3 | DTE3 | ENRX2 | DTE2 | ENRX1 | DTE1 | ENRX0 | DTE0 | ZIST | ZISW | ZISOI |

| RESET  | 0   | 0  | 0  | 0  | 0  | 0     | 0    | 0     | 0    | 0     | 0    | 0     | 0    | 0    | 0    | 0     |

| RW     | RW  | RW | RW | RW | RW | RW    | RW   | RW    | RW   | RW    | RW   | RW    | RW   | R    | R    | R     |

**Table 0-16. Auxiliary Configuration Register Definitions**

| Bits  | Field Name | Description                                                                 |

|-------|------------|-----------------------------------------------------------------------------|

| 15:11 | ///        | Reserved                                                                    |

| 10    | ENRX3      | Enable Receiver Request                                                     |

|       |            | 1 = corresponding CTS/ENRX pin is configured as ENRX.                       |

|       |            | 0 = corresponding CTS/ENRX pin is configured as CTS (default).              |

| 9     | DTE3       | DTE/DCE Channel Configuration                                               |

|       |            | 1 = corresponding serial channel is configured as DTE.                      |

|       |            | 0 = corresponding serial channel is configured as DCE (default).            |

| 8     | ENRX2      | Enable Receiver Request                                                     |

|       |            | 1 = corresponding CTS/ENRX pin is configured as ENRX.                       |

|       |            | 0 = corresponding CTS/ENRX pin is configured as CTS (default).              |

| 7     | DTE2       | DTE/DCE Channel Configuration                                               |

|       |            | 1 = corresponding serial channel is configured as DTE.                      |

|       |            | 0 = corresponding serial channel is configured as DCE (default).            |

| 6     | ENRX1      | Enable Receiver Request                                                     |

|       |            | 1 = corresponding CTS/ENRX pin is configured as ENRX.                       |

|       |            | 0 = corresponding CTS/ENRX pin is configured as CTS (default).              |

| 5     | DTE1       | DTE/DCE Channel Configuration                                               |

|       |            | 1 = corresponding serial channel is configured as DTE.                      |

|       |            | 0 = corresponding serial channel is configured as DCE (default).            |

| 4     | ENRX0      | Enable Receiver Request                                                     |

|       |            | 1 = corresponding CTS/ENRX pin is configured as ENRX.                       |

|       |            | 0 = corresponding CTS/ENRX pin is configured as CTS ( <i>default</i> ).     |

| 3     | DTE0       | DTE/DCE Channel Configuration                                               |

|       |            | 1 = corresponding serial channel is configured as DTE.                      |

|       |            | 0 = corresponding serial channel is configured as DCE (default).            |

| 2     | LSIZ       | Data Bus Width for Accesses to LCS Space                                    |

|       |            | 1 = perform 8-bit accesses.                                                 |

|       |            | 0 = perform 16-bit accesses.                                                |

|       |            | This bit is always 0.                                                       |

| 1     | MSIZ       | Data Bus Width for Accesses Outside the UCS or LCS Address Space, including |

|       |            | the MCS and PCS Address Space                                               |

|       |            | 1 = perform 8-bit accesses.                                                 |

|       |            | 0 = perform 16-bit accesses.                                                |

|       |            | This bit is always 0.                                                       |

| 0     | IOSIZ      | Data Bus Width for All I/O Space Accesses                                   |

|       |            | 1 = perform 8-bit accesses.                                                 |

|       |            | 0 = perform 16-bit accesses.                                                |

|       |            | This bit is always 0.                                                       |

## **System Configuration Register**

The System Configuration register enables MCS0-only mode. It also disables clock output.

Table 0-17. System Configuration Register

| BIT    | 15  | 14     | 13 | 12 | 11 | 10 | 9   | 8   | 7  | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |

|--------|-----|--------|----|----|----|----|-----|-----|----|---|---|---|---|---|---|---|--|

| OFFSET |     |        |    |    |    |    |     | F0h | )h |   |   |   |   |   |   |   |  |

| FIELD  | /// | MCSBIT | CD |    |    |    | /// |     |    |   |   |   |   |   |   |   |  |

| RESET  | 0   | 0      | 0  | 0  | 0  | 0  | 0   | 0   | 0  | 0 | 0 | 0 | 0 | 0 | 0 | 0 |  |

| RW     | RW  | RW     | RW | RW | RW | RW | RW  | RW  | R  | R | R | R | R | R | R | R |  |

|        |     |        |    |    |    |    |     |     | W  | W | W | W | W | W | W | W |  |

**Table 0-18. System Configuration Register Definitions**

| Bits | Field Name | Description                                                                                                                                            |

|------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15   | ///        | Reserved                                                                                                                                               |

| 14   | MCSBIT     | Enable MCS0-Only Mode  1 = the MCS0 pin is active over the entire MCS range.  0 = the MCS0 pin is active for only ¼ of the MCS range.                  |

| 13:9 | ///        | Reserved                                                                                                                                               |

| 8    | CD         | Clock Disable 1 = disable (tri-state) clock output (CPUCLK, pin E14). 0 = enable (tri-state) clock output. PLL clock is driven out on CPUCLK, pin E14. |

| 7:0  | ///        | Reserved                                                                                                                                               |

## **DMA Control Registers**

The DMA Control registers determine the operating mode for the DMA channels. These registers specify whether:

- The destination pointer is memory or I/O space.

- The destination pointer increments, decrements, or keeps constant after each transfer.

- ♦ The source pointer is in memory or I/O space.

- The source pointer increments, decrements, or keeps constant after each transfer.

- DMA activity stops after a programmed number of DMA cycles.

- An interrupt generates with the last transfer

#### These registers also specify:

- The mode of synchronization.

- A DMA channel's relative priority with respect to the other DMA channel.

- Whether Timer 2 DMA requests are enabled or disabled.

- Whether a channel's DMA operations start or stop.

- The data size (bytes or words) of DMA transfers.

Table 0-19. DMA Control Registers

| BIT    | 15   | 14         | 13  | 12   | 11  | 10  | 9  | 8       | 7   | 6  | 5 | 4    | 3   | 2        | 1       | 0   |

|--------|------|------------|-----|------|-----|-----|----|---------|-----|----|---|------|-----|----------|---------|-----|

| OFFSET |      |            |     |      |     |     | DM | A 0 =   | CAh |    |   |      |     |          |         |     |

|        |      |            |     |      |     |     |    | A 1 = 1 |     |    |   |      |     |          |         |     |

|        |      |            |     |      |     |     |    | A 2 =   | -   |    |   |      |     |          |         |     |

|        |      | DMA3 = BAh |     |      |     |     |    |         |     |    |   |      |     |          |         |     |

| FIELD  | OI/W | DEC        | INC | OI/W | DEC | INC | тс | LNI     | SI  | /N | Р | TDRQ | /// | энэм/энэ | ST/STOP | B/W |

| RESET  | 0    | 0          | 0   | 0    | 0   | 0   | 0  | 0       | 0   | 0  | 0 | 0    | 0   | 0        | 0       | 0   |

| RW     | RW   | RW         | RW  | RW   | RW  | R   | R  | R       | R   | R  | R | R    | R   | R        | R       | R   |

|        |      |            |     |      |     | W   | W  | W       | W   | W  | W | W    |     | W        | W       | W   |

**Table 0-20. DMA Control Register Definitions**

| Bits | Field Name | Description                                                                       |

|------|------------|-----------------------------------------------------------------------------------|

| 15   | M/IO       | Destination Pointer                                                               |

|      |            | 0 = destination pointer is in I/O space.                                          |

|      |            | 1 = destination pointer is in memory space.                                       |

| 14   | DEC        | Decrement Destination Pointer                                                     |

|      |            | 1 = decrement destination pointer after each access.                              |

|      |            | Decrement by 1 or 2, depending on whether configured for byte or word operations. |

| 13   | INC        | Increment Destination Pointer                                                     |

|      |            | 1 = increment destination pointer after each access.                              |

|      |            | Increment by 1 or 2, depending on whether configured for byte or word operations. |

| 12   | M/IO       | Source Pointer                                                                    |

|      |            | 0 = source pointer is in I/O space.                                               |

|      |            | 1 = source pointer is in memory space.                                            |

| 11   | DEC        | Source Decrement Pointer                                                          |

|      |            | 1 = decrement source pointer after each access.                                   |

|      |            | Decrement by 1 or 2, depending on whether configured for byte or word operations. |

| Bits | Field Name | Description                                                                           |

|------|------------|---------------------------------------------------------------------------------------|

| 10   | INC        | Source Increment Pointer                                                              |

| 10   |            | 1 = increment source pointer after each access.                                       |

|      |            | Increment by 1 or 2, depending on whether configured for byte or word operations.     |

| 9    | TC         | Transfer Count                                                                        |

| ٦    |            | 1 = DMA operation will end when the Transfer Count register value reaches zero, and   |

|      |            | the ST/STOP bit will also be reset.                                                   |

|      |            | 0 = Transfer Count register decrements on each transfer, but DMA operations do not    |

|      |            | end when the Transfer Count register reaches zero.                                    |

| 8    | INT        | Interrupt Request                                                                     |

|      |            | 1 = generate interrupt request when transfer count ends.                              |

| 7:6  | SYN        | Synchronization                                                                       |

| 1'.0 | OTIV       | Two bits that encode the type of synchronization used.                                |

|      |            | 00 = no external synchronization necessary. DMA transfers can occur at any time.      |

|      |            | Back-to-back DMA bus cycles are performed.                                            |

|      |            | 01 = use source synchronization. DMA transfers occur when the source signals a        |

|      |            | DMA request via the DRQ3-0 signals. Back-to-back DMA bus cycles are performed.        |

|      |            | 10 = use destination synchronization. DMA transfers occur when the destination        |

|      |            | signals a DMA request via the DRQ3-0 signals. After each DMA bus cycle, the           |

|      |            | controller waits 2 clocks before starting another DMA bus cycle. This delay lets the  |

|      |            | destination release its DMA request if it cannot handle another DMA operation and     |

|      |            | gives the microprocessor time to perform a bus cycle between DMA operations.          |

|      |            | 11 = not used.                                                                        |

| 5    | Р          | Priority                                                                              |

|      |            | Determines a channel's priority level relative to other channels.                     |

|      |            | 0 = low priority.                                                                     |

|      |            | 1 = high priority.                                                                    |

|      |            | If two or more channels have simultaneous requests with the same priority level, they |

|      |            | alternate cycles. Default priority among DMA channels is DMA0 (highest), DMA1,        |

|      |            | DMA2, and DMA3 (lowest).                                                              |

| 4    | TDRQ       | DMA Request                                                                           |

|      |            | Enables a channel's DMA request from Timer 2 instead of the external DMA request      |

|      |            | signal.                                                                               |

|      |            | 1 = enable DMA request from Timer 2.                                                  |

|      |            | 0 = disable this feature.                                                             |

| 3    | ///        | Reserved                                                                              |

|      |            | This bit is always set to 0.                                                          |

| 2    | CHG/NCHG   | Enable/Disable Updating of ST/STP Bit                                                 |

|      |            | Writes to the Control Word to enable or disable updating the ST/STP bit.              |

|      |            | 1 = the ST/STP bit in the control word can be changed.                                |

|      |            | 0 = the ST/STP bit in the control word cannot be changed.                             |

|      |            | This bit must be 1 during a write operation to enable writing the ST/STP bit.         |

| 1    | ST/STOP    | DMA Operations                                                                        |

|      |            | Starts and stops a channel's DMA operations.                                          |

|      |            | 1 = start DMA operations.                                                             |

|      |            | 0 = stop DMA operations.                                                              |

|      |            | Bit [2], CHG/NCHG must be 1 during a write operation to write the ST/STP bit.         |

| 0    | B/W        | Data Size of DMA Transfer                                                             |

|      |            | Determines the data size of the DMA transfer.                                         |

|      |            | 1 = enable word transfers.                                                            |

|      |            | 0 = enable byte transfers.                                                            |

|      |            | This bit also determines whether to increment or decrement source and destination     |

|      |            | pointers by 1 (byte) or 2 (word).                                                     |

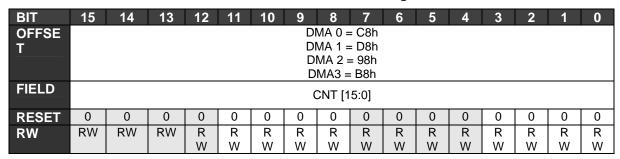

## **DMA Transfer Count Registers**

Each DMA channel has a 16-bit DMA Transfer Count register. This register decrements after each DMA cycle. If the TC bit (bit [9]) in the DMA control word is set, DMA activity ends when the Transfer Count register reaches zero.

**Table 0-21. DMA Transfer Count Registers**

**Table 0-22. DMA Transfer Count Register Definitions**

| Bits | Field Name | Description                 |

|------|------------|-----------------------------|

| 15:0 | CNT [15:0] | 16-bit Transfer Count Value |

### **DMA Destination Address High Registers**

Each DMA channel has a 24-bit Destination register and a 24-bit Source register. Each 24-bit address occupies two 16-bit registers (the High register and the Low register) in the PCB. For each DMA channel to be used, all four Address registers for that channel must be initialized. These addresses can individually increment or decrement after each transfer.

- If word transfers are performed, the address increments or decrements by 2 after each transfer.

- If byte transfers are performed, the address increments or decrements by 1.

Each register can point into either memory or I/O space. You must program the upper eight bits to all '0's to address the normal 64K I/O space. Since the DMA channels can perform transfers to or from odd addresses, there is no restriction on values for the Destination and Source Address registers. However, DSTni can achieve higher transfer rates by performing all word transfers to or from even addresses, so that accesses occur in single 16-bit bus cycles.

Table 0-23. DMA Destination Address High Registers

| BIT    | 15  | 14  | 13  | 12  | 11  | 10  | 9   | 8     | 7         | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|--------|-----|-----|-----|-----|-----|-----|-----|-------|-----------|---|---|---|---|---|---|---|

| OFFSET |     |     |     |     |     |     |     | DMA ( |           |   |   |   |   |   |   |   |

|        |     |     |     |     |     |     |     | DMA 1 | -         |   |   |   |   |   |   |   |

|        |     |     |     |     |     |     |     | DMA 2 |           |   |   |   |   |   |   |   |

|        |     |     |     |     |     |     |     | DMA3  | = B6r     | 1 |   |   |   |   |   |   |