# VPC3+C User Manual

**Revision 3.04**

#### **Liability Exclusion**

We have tested the contents of this document regarding agreement with the hardware and software described. Nevertheless, there may be deviations and we do not guarantee complete agreement. The data in the document is tested periodically, however. Required corrections are included in subsequent versions. We gratefully accept suggestions for improvements.

#### Copyright

Copyright © profichip GmbH 2004-2014. All Rights Reserved. Unless permission has been expressly granted, passing on this document or copying it, or using and sharing its content are not allowed. Offenders will be held liable. All rights reserved, in the event a patent is granted or a utility model or design is registered.

This document is subject to technical changes.

## **Table of Contents**

| 1 | Intr                     | Introduction5                                                                                                                                                                                                                                                                                                                                    |                                                                |  |  |  |  |

|---|--------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|--|--|--|--|

| 2 | Fur                      | nctional Description                                                                                                                                                                                                                                                                                                                             | 7                                                              |  |  |  |  |

|   | 2.1                      | Overview                                                                                                                                                                                                                                                                                                                                         | 7                                                              |  |  |  |  |

| 3 | Pin                      | Description                                                                                                                                                                                                                                                                                                                                      | 9                                                              |  |  |  |  |

|   | 3.1                      | -                                                                                                                                                                                                                                                                                                                                                |                                                                |  |  |  |  |

|   | 3.2                      | Pinout                                                                                                                                                                                                                                                                                                                                           |                                                                |  |  |  |  |

| 4 | Me                       | mory Organization                                                                                                                                                                                                                                                                                                                                | .13                                                            |  |  |  |  |

|   | 4.1<br>4.2<br>4.3        | Overview<br>Control Parameters (Latches/Registers)<br>Organizational Parameters (RAM)                                                                                                                                                                                                                                                            | 15                                                             |  |  |  |  |

| 5 | ASI                      | C Interface                                                                                                                                                                                                                                                                                                                                      | .19                                                            |  |  |  |  |

|   | 5.1<br>5.2<br>5.3<br>5.4 | Mode Registers5.1.1Mode Register 05.1.2Mode Register 15.1.3Mode Register 25.1.4Mode Register 3Status RegisterInterrupt Controller5.3.1Interrupt Request Register5.3.2Interrupt Acknowledge / Mask RegisterWatchdog Timer5.4.1Automatic Baud Rate Identification5.4.2Baud Rate Monitoring5.4.3Response Time Monitoring                            | 19<br>21<br>23<br>25<br>26<br>28<br>29<br>32<br>32<br>33<br>33 |  |  |  |  |

| 6 | PR                       | OFIBUS DP Interface                                                                                                                                                                                                                                                                                                                              | .35                                                            |  |  |  |  |

|   | 6.1<br>6.2               | DP Buffer Structure<br>Description of the DP Services<br>6.2.1 Set_Slave_Add (SAP 55)<br>6.2.2 Set _Prm (SAP 61)<br>6.2.3 Chk_Cfg (SAP 62)<br>6.2.4 Slave_Diag (SAP 60)<br>6.2.5 Write_Read_Data / Data_Exchange (Default_SAP)<br>6.2.6 Global_Control (SAP 58)<br>6.2.7 RD_Input (SAP 56)<br>6.2.8 RD_Output (SAP 57)<br>6.2.9 Get_Cfg (SAP 59) | 38<br>39<br>43<br>44<br>46<br>50<br>51<br>51                   |  |  |  |  |

| 7  | PRC                                          | OFIBUS DP Extensions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 53                                                                        |

|----|----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|

|    | 7.1<br>7.2                                   | Set_(Ext_)Prm (SAP 53 / SAP 61)<br>PROFIBUS DP-V1<br>7.2.1 Acyclic Communication Relationships<br>7.2.2 Diagnosis Model                                                                                                                                                                                                                                                                                                                                                                                                       | .54<br>.54<br>.57                                                         |

|    | 7.3                                          | PROFIBUS DP-V27.3.1DXB (Data eXchange Broadcast)7.3.2IsoM (Isochron Mode)7.3.3CS (Clock Synchronization)                                                                                                                                                                                                                                                                                                                                                                                                                      | .58<br>.64                                                                |

| 8  | Har                                          | dware Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 75                                                                        |

|    | 8.1<br>8.2<br>8.3<br>8.4                     | Universal Processor Bus Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | .75<br>.79<br>.81<br>.82<br>.83<br>.83<br>.83                             |

| 9  | PRC                                          | OFIBUS Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 85                                                                        |

|    | 9.1<br>9.2                                   | Pin Assignment<br>Example for the RS485 Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                           |

| 10 | Оре                                          | erational Specifications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 87                                                                        |

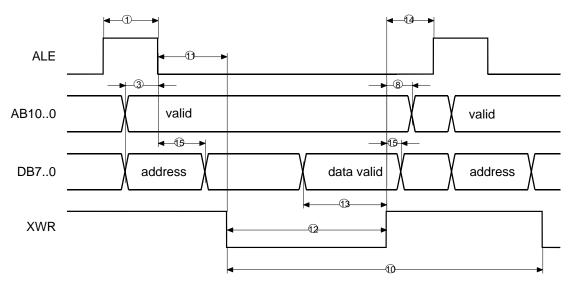

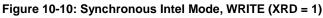

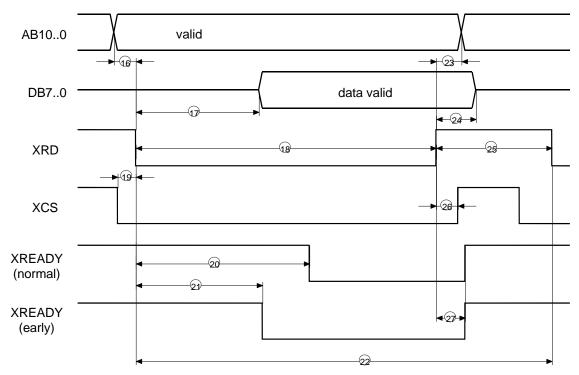

|    | 10.2<br>10.3<br>10.4<br>10.5<br>10.6<br>10.7 | Absolute Maximum Ratings<br>Recommended Operating Conditions<br>General DC Characteristics<br>Ratings for the Output Drivers<br>DC Electrical Characteristics Specification for 5V Operation<br>DC Electrical Characteristics Specification for 3.3V Operation .<br>Timing Characteristics<br>10.7.1 System Bus Interface<br>10.7.2 Timing in the Synchronous Intel Mode<br>10.7.3 Timing in the Asynchronous Intel Mode<br>10.7.4 Timing in the Synchronous Motorola Mode<br>10.7.5 Timing in the Asynchronous Motorola Mode | .87<br>.88<br>.88<br>.89<br>.90<br>.90<br>.90<br>.91<br>.93<br>.95<br>.97 |

|    |                                              | Processing Instructions1<br>Ordering Information1                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                           |

Profichip's **VPC3+C** is a communication chip with processor interface for intelligent PROFIBUS DP-Slave applications. It's an enhancement of the **VPC3+B** in terms of protocol functions and power consumption.

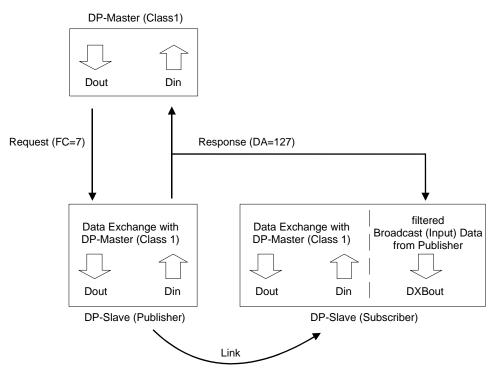

The VPC3+C handles the message and address identification, the data security sequences and the protocol processing for PROFIBUS DP. In addition the acyclic communication and alarm messages, described in DP-V1 extension, are supported. Furthermore the slave-to-slave communication Data eXchange Broadcast (DXB) and the Isochronous Bus Mode (IsoM), described in DP-V2 extension, are also provided.

Automatic recognition and support of data transmissions rates up to 12 Mbit/s, the integration of the complete PROFIBUS DP protocol, 4K Byte communication RAM and the configurable processor interface are features to create high-performance PROFIBUS DP-Slave applications. The device can be operated with either 3.3V or 5V single supply voltage.

Profichip's **VPC3+** is the predecessor of VPC3+C and VPC3+B. **VPC3+** and **VPC3+C** are pin-compatible. Therefore VPC3+ can be replaced by VPC3+C in existing applications without any restrictions or SWmodifications. However, downgrading from VPC3+C to VPC3+ is only possible, if the additional features of VPC3+C (4K Byte RAM, DP-V1- or DP-V2-functionality, 3.3V supply) are not used.

As there are also simple devices in the automation engineering area, such as switches or thermoelements, that do not require a microcontroller for data preprocessing, profichip offers a DP-Slave ASIC with 32 direct input/output bits. The **VPCLS2** handles the entire data traffic independently. No additional microprocessor or firmware is necessary. The VPCLS2 is compatible to existing chips.

Further information about our products or current and future projects is available on our web page: <u>http://www.profichip.com</u>.

Notes:

#### 2.1 Overview

The VPC3+C makes a cost optimized design of intelligent PROFIBUS DP-Slave applications possible.

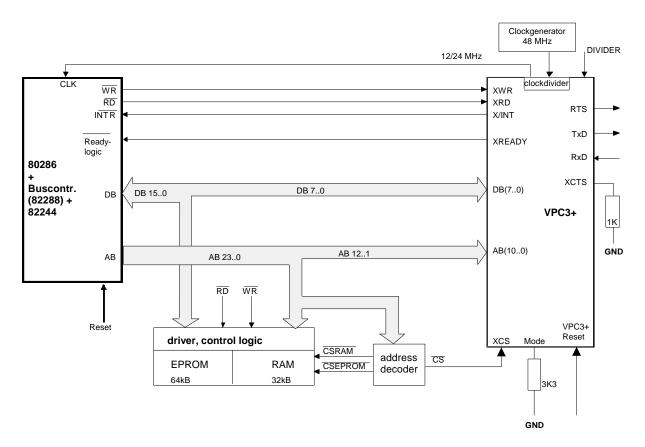

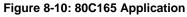

The processor interface supports the following processor series:

| Intel:    | 80C31, 80X86                  |

|-----------|-------------------------------|

| Siemens:  | 80C166/165/167                |

| Motorola: | HC11-, HC16-, and HC916 types |

The VPC3+C handles the physical layer 1 and the data link layer 2 of the ISO/OSI-reference-model excluding the analog RS485 drivers.

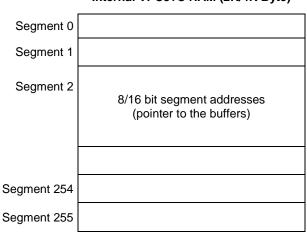

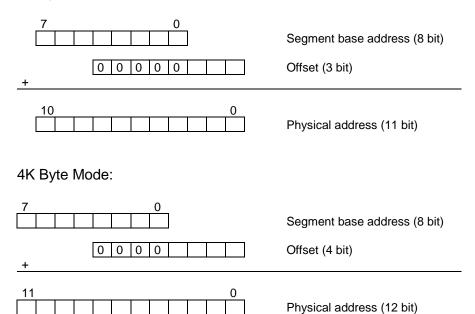

The **integrated 4K Byte Dual-Port-RAM** serves as an interface between the VPC3+C and the software/application. In case of using 2K Byte the entire memory is divided into 256 segments, with 8 bytes each. Otherwise in the 4K Byte mode the segment base addresses starts at multiple of 16. Addressing by the user is done directly, however, the internal Micro Sequencer (MS) addresses the RAM by means of the so-called basepointer. The base-pointer can be positioned at the beginning of a segment in the memory. Therefore, all buffers must be located at the beginning of a segment.

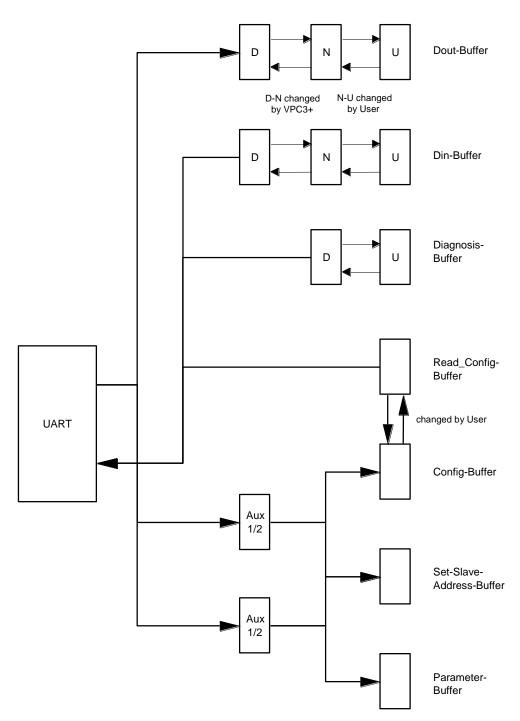

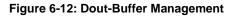

If the VPC3+C carries out a DP communication it automatically sets up all DP-SAPs. The various telegram information are made available to the user in separate data buffers (for example, parameter and configuration data). Three buffers are provided for data communication (three for output data and three for input data). As one buffer is always available for communication no resource problems can occur. For optimal diagnosis support, the VPC3+C offers two Diagnosis-Buffers. The user enters the updated diagnosis data into these buffers. One Diagnosis-Buffer is always assigned to the VPC3+C.

The **Bus Interface Unit** is a parameterizable synchronous/asynchronous 8bit interface for various Intel and Motorola microcontrollers/processors. The user can directly access the internal 2K/4K Byte RAM or the parameter latches and control registers via the 11/12-bit address bus.

Procedure-specific parameters (Station\_Address, control bits, etc.) must be transferred to the **Parameter Registers** and to the **Mode Registers** after power-on.

The MAC status can be observed at any time in the Status Register.

Various events (e.g. various indications, error events, etc.) are entered in the **Interrupt Controller**. These events can be individually enabled via a mask register. Acknowledgement takes place by means of the acknowledge register. The VPC3+C has a common interrupt output.

### **2** Functional Description

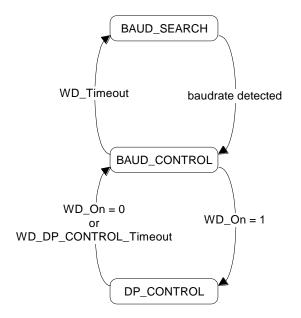

The integrated **Watchdog Timer** is operated in three different states: BAUD\_SEARCH, BAUD\_CONTROL and DP\_CONTROL.

The **Micro Sequencer** (MS) controls the entire process. It contains the DP-Slave state machine (DP\_SM).

The integrated **4K Byte RAM** that operates as a Dual-Port-RAM contains procedure-specific parameters (buffer pointer, buffer lengths, Station\_Address, etc.) and the data buffers.

In the **UART**, the parallel data flow is converted into the serial data flow and vice-versa. The VPC3+C is capable of automatically identifying the baud rates (9.6 Kbit/s - 12 Mbit/s).

The **Idle Timer** directly controls the bus times on the serial bus line.

Pin Description 3

### 3.1 Pin Assignment

| Pin | Signal Name   | In/Out | Description                                                  |                                                                                   |                                                    | Source / Destination          |

|-----|---------------|--------|--------------------------------------------------------------|-----------------------------------------------------------------------------------|----------------------------------------------------|-------------------------------|

| 1   | XCS           | I(C)   | Chip-Select                                                  | C32 Mode (2<br>C165 Mode:                                                         | K Byte RAM): connect to VDD<br>CS-Signal           | CPU (80C165)                  |

|     | AB11          | (-)    | Address Bus 11 (C                                            | Address Bus 11 (C32-Mode; 4K Byte RAM)                                            |                                                    |                               |

|     | XWR / E_CLOCK |        | Write Signal / E_C                                           |                                                                                   |                                                    |                               |

| 2   | AB11          | I(C)   | Address Bus 11 (A                                            | Address Bus 11 (Asynchronous Motorola Mode; 4K Byte RAM)                          |                                                    |                               |

| 3   | DIVIDER       | I(C)   | Setting the scaling factor for CLKOUT                        | 2/4                                                                               | '0' = CLK divided by 4<br>'1' = CLK divided by 2   | Configuration Pin             |

| 4   | XRD / R_W     | I(C)   | Read Signal / Read                                           | d_Write for Me                                                                    | otorola                                            | CPU                           |

| 5   | CLK           | I(TS)  | System Clock Input                                           | t, 48 MHz                                                                         |                                                    | System                        |

| 6   | VSS           |        |                                                              |                                                                                   |                                                    |                               |

| 7   | CLKOUT2/4     | 0      | Clock Output (Syst                                           | em Clock divid                                                                    | led by 2 or 4)                                     | System, CPU                   |

| 8   | XINT/MOT      | I(C)   | '0' = Intel Interface<br>'1' = Motorola Inter                | face                                                                              |                                                    | Configuration Pin             |

| 9   | X/INT         | 0      | Interrupt                                                    |                                                                                   |                                                    | CPU; Interrupt-<br>Controller |

| 10  | AB10          | I(CPD) | Address Bus                                                  | C32 Mode:<br>C165 Mode:                                                           | ʻ0'<br>Address Bus                                 | System, CPU                   |

| 11  | DB0           | I(C)/O | Data Bus                                                     | C32 Mode:                                                                         | Data/Address Bus multiplexed                       | CPU, Memory                   |

| 12  | DB1           | I(C)/O | Data Bus                                                     | C165 Mode: Data/Address Bus separated                                             |                                                    | CPU, Memory                   |

| 13  | XDATAEXCH     | 0      | Indicates DATA-EX                                            | CH state for F                                                                    | PROFIBUS DP                                        | LED                           |

| 15  | SYNC          | 0      | Synchronization Signal for Isochron Mode (see section 8.3.2) |                                                                                   |                                                    | CPU                           |

| 14  | XREADY/XDTACK | 0      | Ready for external CPU                                       |                                                                                   |                                                    | System, CPU                   |

| 15  | DB2           | I(C)/O | Data Bus                                                     | C32 mode:                                                                         | Data /Address Bus multiplexed                      | CPU, Memory                   |

| 16  | DB3           | I(C)/O | Data Bus                                                     | C165 mode:                                                                        | Data/Address Bus separate                          | CF 0, Memory                  |

| 17  | VSS           |        |                                                              |                                                                                   |                                                    |                               |

| 18  | VDD           |        |                                                              |                                                                                   |                                                    |                               |

| 19  | DB4           | I(C)/O |                                                              |                                                                                   |                                                    |                               |

| 20  | DB5           | I(C)/O | Data Bus                                                     | C32 mode:                                                                         | Data/Address Bus multiplexed                       | CPU, Memory                   |

| 21  | DB6           | I(C)/O | Data Bus                                                     | C165 mode:                                                                        | Data/Address Bus separate                          | CF 0, Memory                  |

| 22  | DB7           | I(C)/O |                                                              |                                                                                   |                                                    |                               |

| 23  | MODE          | I      |                                                              |                                                                                   | eparated; Ready Signal<br>ultiplexed, fixed Timing | Configuration Pin             |

| 24  | ALE / AS      |        | Address Latch<br>Enable                                      | C32 mode:<br>C165 mode:                                                           | ALE<br>'0' (2K Byte RAM)                           | CPU                           |

| 24  | AB11          | I(C)   |                                                              | Address Bus 11 (Asynchronous Intel and<br>Synchronous Motorola Mode; 4K Byte RAM) |                                                    |                               |

| 25  | AB9           | I      | Address Bus                                                  | C32 Mode:<br>C165 Mode:                                                           | <log>0<br/>Address Bus</log>                       | CPU, Memory                   |

| 26  | TXD           | 0      | Serial Transmit Port (external pull-up resistor required)    |                                                                                   |                                                    | PROFIBUS Interface            |

| 27  | RTS           | 0      | Request to Send                                              |                                                                                   |                                                    | PROFIBUS Interface            |

| 28  | VSS           |        |                                                              |                                                                                   |                                                    |                               |

| 29  | AB8           | I(C)   | Address Bus                                                  | C32 mode:<br>C165 mode:                                                           | ʻ0'<br>Address Bus                                 | CPU, Memory                   |

Copyright © profichip GmbH 2014

### **3 Pin Description**

| Pin | Signal Name | In/Out | Description                              | Source / Destination |

|-----|-------------|--------|------------------------------------------|----------------------|

| 30  | RXD         | I(C)   | Serial Receive Port                      | PROFIBUS Interface   |

| 31  | AB7         | I(C)   | Address Dus                              |                      |

| 32  | AB6         | I(C)   | Address Bus                              | CPU, Memory          |

| 33  | XCTS        | I(C)   | Clear to Send: '0' = send enable         | FSK Modem            |

| 34  | XTEST0      | I(C)   | Pin must be connected to VDD.            |                      |

| 35  | XTEST1      | I(C)   | Pin must be connected to VDD.            |                      |

| 36  | RESET       | I(CS)  | Connect Reset Input with CPU's port pin. |                      |

| 37  | AB4         | I(C)   | Address Bus                              | CPU, Memory          |

| 38  | VSS         |        |                                          |                      |

| 39  | VDD         |        |                                          |                      |

| 40  | AB3         | I(C)   |                                          |                      |

| 41  | AB2         | I(C)   |                                          |                      |

| 42  | AB5         | I(C)   | Address Bus                              | CPU, Memory          |

| 43  | AB1         | I(C)   | ]                                        |                      |

| 44  | AB0         | I(C)   | 1                                        |                      |

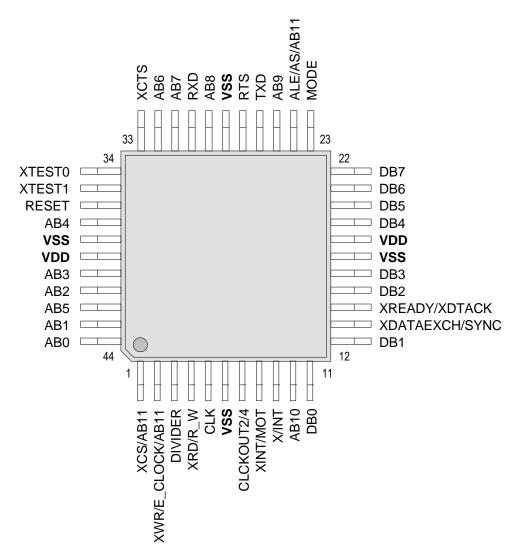

#### Figure 3-1: Pin Assignment

Notes: All signals that begin with X.. are LOW active. C32-Mode means 'Synchronous Intel Mode' and C165-Mode means 'Asynchronous Intel Mode'. VDD = +5 V VSS = 0 V

#### Input Levels:

| CMOS                  |

|-----------------------|

| CMOS, Schmitt-Trigger |

| CMOS, pulldown        |

| TTL, Schmitt-Trigger  |

|                       |

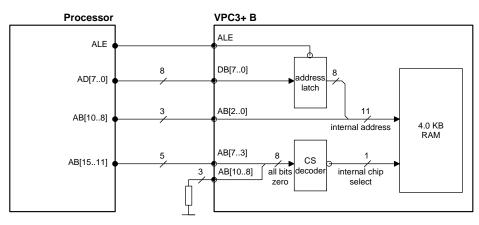

#### 4K Byte RAM extension

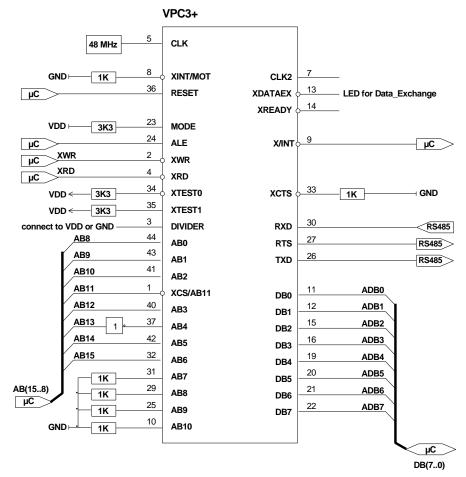

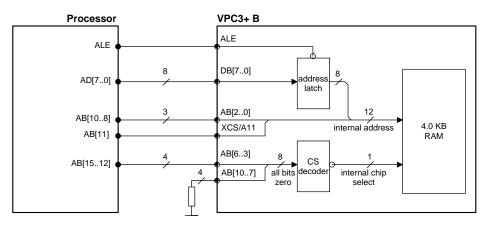

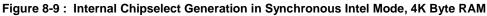

Beginning with Step B of the VPC3+ the communication RAM has been extended to 4K Byte, whereas Step A only has 2K Byte. To access the entire 4K Byte RAM in VPC3+C an additional address signal AB11 is required. Which pin is assigned to A11 depends on the Processor Interface Mode used (see Figure 3-2). Due to compatibility reasons the pin which is now assigned to A11 was unused in Step A for the certain Interface Mode.

| Processor Interface Mode   | Pin | Signal Name |

|----------------------------|-----|-------------|

| Synchronous Intel Mode     | 1   | XCS         |

| Asynchronous Intel Mode    | 24  | ALE/AS      |

| Asynchronous Motorola Mode | 2   | XWR/E_CLOCK |

| Synchronous Motorola Mode  | 24  | ALE/AS      |

#### Figure 3-2 : Pin assignment for AB11

The 4K Byte RAM extension must be enabled in Mode Register 2 (see section 5.1.3). By default the 4K Byte mode is disabled.

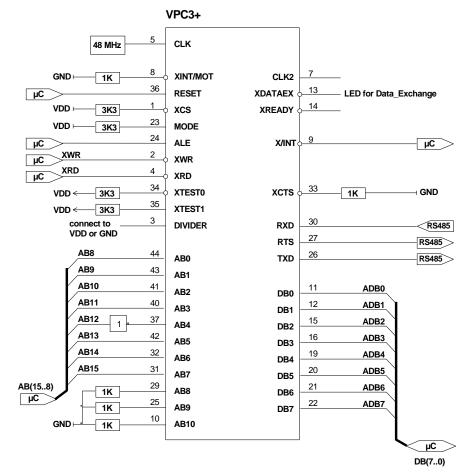

### 3.2 Pinout

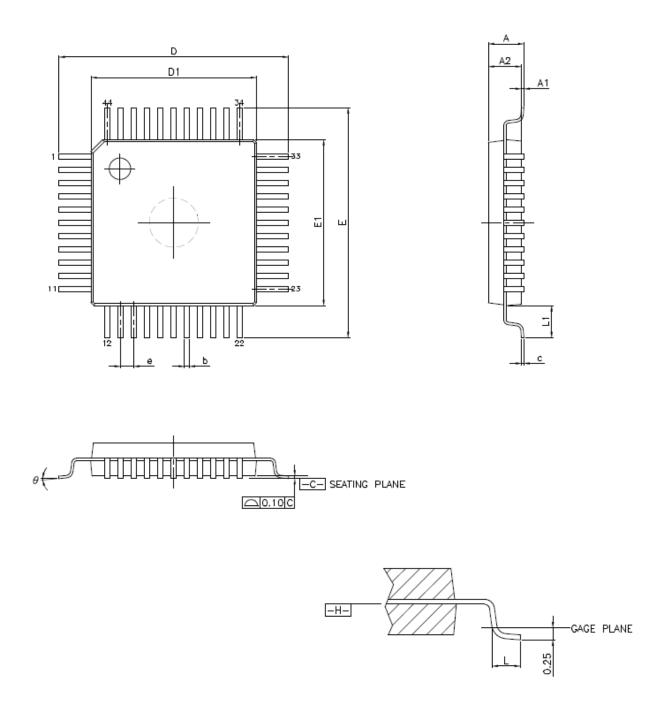

VPC3+C has a 44-pin PQFP housing with the following pinout:

Figure 3-3: VPC3+C Pinout

For details about package outline and dimensions see section 10.8.

### **3 Pin Description**

Notes:

#### 4.1 Overview

The internal Control Parameters are located in the first 21 addresses. The latches/registers either come from the internal controller or influence the controller. Certain cells are read- or write-only. The internal working cells, which are not accessible by the user, are located in RAM at the same address locations.

The Organizational Parameters are located in RAM beginning with address 16H. The entire buffer structure (for the DP-SAPs) is based on these parameters. In addition, general parameter data (Station\_Address, Ident\_Number, etc.) and status information (Global\_Control command, etc.) are also stored in these cells.

Corresponding to the parameter setting of the Organizational Parameters, the user-generated buffers are located beginning with address 40H. All buffers or lists must begin at segment addresses (8 bytes segmentation for 2K Byte mode, 16 bytes segmentation for 4K Byte mode).

| Address           | Function                           |                                                                                                                                                                |                        |  |

|-------------------|------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|--|

| 000H<br>:<br>015H | Control Parame<br>(latches/registe |                                                                                                                                                                | Internal working cells |  |

| 016H<br>:<br>03FH | Organizational                     |                                                                                                                                                                |                        |  |

| 040H<br>:         | DP-buffers:<br>DP-V1-buffer:       | Data in (3)*<br>Data out (3)**<br>Diagnosis data(2)<br>Parameter data (1)<br>Configuration data (2)<br>Auxiliary buffers (2)<br>SSA-buffer (1)<br>SAP-List (1) |                        |  |

| 7FFH (FFFH)       | DP-V2-buffer:                      | DXB-List (1)<br>Indication / Response bu<br>DXB out (3)****<br>DXB-buffers (2)<br>CS-buffers (1)                                                               | ffers ***              |  |

#### Figure 4-1: Memory Table

- \* Data in means input data from DP-Slave to DP-Master

- \*\* Data out means output data from DP-Master to DP-Slave

- \*\*\* number of buffers depends on the entries in the SAP-List

- \*\*\*\* DXB out means input data from another DP-Slave (slave-to-slave communication)

### 4 Memory Organization

Internal VPC3+C RAM (2K/4K Byte)

Building of the physical buffer address:

2K Byte Mode:

### 4.2 Control Parameters (Latches/Registers)

These cells can be either read-only or write-only. In the Motorola Mode the VPC3+C carries out 'address swapping' for an access to the address locations 00H - 07H (word registers). That is, the VPC3+C internally generates an even address from an odd address and vice-versa.

| Address |      |                       |         |                                                                                                     |

|---------|------|-----------------------|---------|-----------------------------------------------------------------------------------------------------|

| Intel   | Mot. |                       | Bit No. | Significance (Read Access!)                                                                         |

| 00H     | 01H  | Int-Req-Reg           | 70      |                                                                                                     |

| 01H     | 00H  | Int-Req-Reg           | 158     | Interrupt Controller Register                                                                       |

| 02H     | 03H  | Int-Reg               | 70      |                                                                                                     |

| 03H     | 02H  | Int-Reg               | 158     |                                                                                                     |

| 04H     | 05H  | Status-Reg            | 70      | Status Register                                                                                     |

| 05H     | 04H  | Status-Reg            | 158     |                                                                                                     |

| 06H     | 07H  | Mode-Reg 0            | 70      | Mode Register 0                                                                                     |

| 07H     | 06H  | Mode-Reg 0            | 158     |                                                                                                     |

| 80      | βH   | Din_Buffer_SM         | 70      | Buffer assignment of the<br>DP_Din_Buffer_State_Machine                                             |

| 09      | H    | New_Din_Buffer_Cmd    | 10      | The user makes a new DP Din_Buf available in the N state.                                           |

| 0A      | Ή    | Dout_Buffer_SM        | 70      | Buffer assignment of the<br>DP_Dout_Buffer_State_Machine                                            |

| 0E      | ВН   | Next_Dout_Buffer_Cmd  | 30      | The user fetches the last DP<br>Dout_Buf from the N state                                           |

| 0C      | н    | Diag_Buffer_SM        | 30      | Buffer assignment for the<br>DP_Diag_Buffer_State_Machine                                           |

| 0E      | ЭН   | New_Diag_Buffer_Cmd   | 10      | The user makes a new DP<br>Diag_Buf available to the VPC3+C.                                        |

| 0E      | ΞH   | User_Prm_Data_Okay    | 10      | The user positively acknowledges<br>the user parameter setting data of a<br>Set_(Ext_)Prm telegram. |

| 0F      | Ή    | User_Prm_Data_Not_Oka | ay 10   | The user negatively acknowledges<br>the user parameter setting data of a<br>Set_(Ext_)Prm telegram. |

| 10      | Н    | User_Cfg_Data_Okay    | 10      | The user positively acknowledges the configuration data of a Chk_Cfg telegram.                      |

| 11H     |      | User_Cfg_Data_Not_Oka | y 10    | The user negatively acknowledges the configuration data of a Chk_Cfg telegram.                      |

| 12H     |      | DXBout_Buffer_SM      | 70      | Buffer assignment of the<br>DXBout_Buffer_State_Machine                                             |

| 13H     |      | Next_DXBout_Buffer_Cm | d 20    | The user fetches the last<br>DXBout Buf from the N state                                            |

| 14H     |      | SSA_Buffer_Free_Cmd   |         | The user has fetched the data from the SSA_Buf and enables the buffer again.                        |

| 15      | iΗ   | Mode-Reg 1            | 70      |                                                                                                     |

Figure 4-2: Assignment of the Internal Parameter-Latches for READ

### 4 Memory Organization

| Add<br>Intel | ress<br>Mot. | Name                     | Bit No. | Significance (Write Access!)                                |

|--------------|--------------|--------------------------|---------|-------------------------------------------------------------|

| 00H          | 01H          | Int-Req-Reg              | 70      |                                                             |

| 01H          | 00H          | Int-Req_Reg              | 158     |                                                             |

| 02H          | 03H          | Int-Ack-Reg              | 70      | Interrupt Controller Degister                               |

| 03H          | 02H          | Int-Ack-Reg              | 158     | Interrupt-Controller-Register                               |

| 04H          | 05H          | Int–Mask-Reg             | 70      |                                                             |

| 05H          | 04H          | Int-Mask-Reg             | 158     |                                                             |

| 06H          | 07H          | Mode-Reg0                | 70      | Setting parameters for individual bits                      |

| 07H          | 06H          | Mode-Reg0                | 158     | Setting parameters for individual bits                      |

| 08           | зн           | Mode-Reg1-S              | 70      |                                                             |

| 09           | ЭH           | Mode-Reg1-R              | 70      |                                                             |

| 0A           | ٨H           | WD_BAUD_CONTROL_V        | √al 70  | Square-root value for<br>baud rate monitoring               |

| OE           | ЗH           | minT <sub>SDR</sub> _Val | 70      | minT <sub>SDR</sub> time                                    |

| 00           | СН           | Mode-Reg2                | 70      | Mode Register 2                                             |

| 00           | ЭН           | Sync_PW_Reg              | 70      | Sync Pulse Width Register                                   |

| OE           | ΞH           | Control_Command_Reg      | 70      | Control_Command value for<br>comparison with SYNCH telegram |

| 0FH          |              | Group_Select_Reg         | 70      | Group_Select value for comparison<br>with SYNCH telegram    |

| 10           | )H           | Reserved                 |         |                                                             |

| 11H          |              |                          |         |                                                             |

| 12H          |              | Mode-Reg3                | 70      | Mode Register 3                                             |

| 13           | 3H           |                          |         |                                                             |

| 14           | 4H           | Reserved                 |         |                                                             |

| 15           | 5H           |                          |         |                                                             |

Figure 4-3: Assignment of the Internal Parameter-Latches for WRITE

### 4.3 Organizational Parameters (RAM)

The user stores the organizational parameters in the RAM under the specified addresses. These parameters can be written and read.

| Add        |      |                   |         |                                                                                                                        |

|------------|------|-------------------|---------|------------------------------------------------------------------------------------------------------------------------|

| Intel      | Mot. | Name              | Bit No. |                                                                                                                        |

| 16H        |      | R_TS_Adr          |         | Setup Station_Address of the VPC3+C                                                                                    |

| 17         | Ϋ́H  | SAP_List_Ptr      |         | Pointer to a RAM address which is preset with FFh or to SAP-List                                                       |

| 18H        | 19H  | R_User_WD_Value   | 70      | In DP_Mode an internal 16-bit watchdog                                                                                 |

| 19H        | 18H  | R_User_WD_Value   | 158     | timer monitors the user.                                                                                               |

| 1 <i>A</i> | λH   | R_Len_Dout_Buf    |         | Length of the 3 Dout_Buf                                                                                               |

| 1E         | зн   | R_Dout_Buf_Ptr1   |         | Segment base address of Dout_Buf 1                                                                                     |

| 10         | ЭН   | R_Dout_Buf_Ptr2   |         | Segment base address of Dout_Buf 2                                                                                     |

| 10         | ЭН   | R_Dout_Buf_Ptr3   |         | Segment base address of Dout_Buf 3                                                                                     |

| 1E         | ΕH   | R_Len_Din_Buf     |         | Length of the 3 Din_Buf                                                                                                |

| 1F         | ΞH   | R_Din_Buf_Ptr1    |         | Segment base address of Din_Buf 1                                                                                      |

| 20         | )H   | R_Din_Buf_Ptr2    |         | Segment base address of Din_Buf 2                                                                                      |

| 21         | Н    | R_Din_Buf_Ptr3    |         | Segment base address of Din_Buf 3                                                                                      |

| 22         | 2H   | R_Len_DXBout_Buf  |         | Length of the 3 DXBout_Buf                                                                                             |

| 23         | вн   | R_DXBout_Buf_Ptr1 |         | Segment base address of DXBout_Buf 1                                                                                   |

| 24         | ιH   | R_Len Diag_Buf1   |         | Length of Diag_Buf 1                                                                                                   |

| 25H        |      | R_Len Diag_Buf2   |         | Length of Diag_Buf 2                                                                                                   |

| 26         | бH   | R_Diag_Buf_Ptr1   |         | Segment base address of Diag_Buf 1                                                                                     |

| 27         | Ή    | R_Diag_Buf_Ptr2   |         | Segment base address of Diag_Buf 2                                                                                     |

| 28H        |      | R_Len_Cntrl_Buf1  |         | Length of Aux_Buf 1 and the<br>corresponding control buffer, for example<br>SSA_Buf, Prm_Buf, Cfg_Buf,<br>Read_Cfg_Buf |

| 29H        |      | R_Len_Cntrl_Buf2  |         | Length of Aux_Buf 2 and the<br>corresponding control buffer, for example<br>SSA_Buf, Prm_Buf, Cfg_Buf,<br>Read_Cfg_Buf |

| 2AH        |      | R_Aux_Buf_Sel     |         | Bit array; defines the assignment of the<br>Aux_Buf 1 and 2 to the control buffers<br>SSA_Buf, Prm_Buf, Cfg_Buf        |

| 2BH        |      | R_Aux_Buf_Ptr1    |         | Segment base address of Aux_Buf 1                                                                                      |

| 2CH        |      | R_Aux_Buf_Ptr2    |         | Segment base address of Aux_Buf 2                                                                                      |

| 2DH        |      | R_Len_SSA_Data    |         | Length of the input data in the<br>Set_Slave_Address_Buf                                                               |

| 2EH        |      | R_SSA_Buf_Ptr     |         | Segment base address of the<br>Set_Slave_Address_Buf                                                                   |

| 2F         | Ή    | R_Len_Prm_Data    |         | Length of the input data in the Prm_Buf                                                                                |

### 4 Memory Organization

| Address<br>Intel Mot. | Name Bit No.         | Significance                                                                                                                    |

|-----------------------|----------------------|---------------------------------------------------------------------------------------------------------------------------------|

| 30H                   | R_Prm_Buf_Ptr        | Segment base address of the Prm_Buf                                                                                             |

| 31H                   | R_Len_Cfg_Data       | Length of the input data in the Cfg_Buf                                                                                         |

| 32H                   | R_Cfg_Buf_Ptr        | Segment base address of the Cfg_Buf                                                                                             |

| 33H                   | R_Len_Read_Cfg_Data  | Length of the input data in the<br>Read_Cfg_Buf                                                                                 |

| 34H                   | R_Read_Cfg_Buf_Ptr   | Segment base address of the<br>Read_Cfg_Buf                                                                                     |

| 35H                   | R_Len_DXB_Link_Buf   | Length of the DXB_Linktable                                                                                                     |

| 36H                   | R_DXB_Link_Buf_Ptr   | Segment base address of the<br>DXB_Link_Buf                                                                                     |

| 37H                   | R_Len_DXB_Status_Buf | Length of the DXB_Status                                                                                                        |

| 38H                   | R_DXB_Status_Buf_Ptr | Segment base address of the<br>DXB_Status_Buf                                                                                   |

| 39H                   | R_Real_No_Add_Change | This parameter specifies whether the Station_Address may be changed again later.                                                |

| ЗАН                   | R_Ident_Low          | The user sets the parameters for the Ident_Number_Low value.                                                                    |

| ЗВН                   | R_Ident_High         | The user sets the parameters for the<br>Ident_Number_High value.                                                                |

| 3CH                   | R_GC_Command         | The Control_Command of Global_Control last received                                                                             |

| 3DH                   | R_Len_Spec_Prm_Buf   | If parameters are set for the<br>Spec_Prm_Buffer_Mode (see Mode<br>Register 0), this cell defines the length of<br>the Prm_Buf. |

| 3EH                   | R_DXBout_Buf_Ptr2    | Segment base address of DXBout_Buf 2                                                                                            |

| 3FH                   | R_DXBout_Buf_Ptr3    | Segment base address of DXBout_Buf 3                                                                                            |

Figure 4-4: Assignment of the Organizational Parameters

### 5.1 Mode Registers

In the VPC3+C parameter bits that access the controller directly or which the controller directly sets are combined in three Mode Registers (0, 1, 2 and 3).

#### 5.1.1 Mode Register 0

Setting parameters for Mode Register 0 may take place in the Offline state only (for example, after power-on). The VPC3+C may not exit the Offline state until Mode Register 0, all Control and Organizational Parameters are loaded (START\_VPC3 = 1 in Mode Register 1).

| Address        |                      |                   | Decignotion |         |                 |         |                      |                       |                                              |

|----------------|----------------------|-------------------|-------------|---------|-----------------|---------|----------------------|-----------------------|----------------------------------------------|

| Address        | 7                    | 6                 | 5           | 4       | 3               | 2       | 1                    | 0                     | Designation                                  |

| 06H<br>(Intel) | Freeze_<br>Supported | Sync<br>Supported | Early_Rdy   | Int_Pol | CS<br>Supported | WD_Base | Dis_Stop_<br>Control | Dis_Start_<br>Control | Mode Reg 0<br>7 0<br>See below for<br>coding |

| Address        |          |                      | Designation            |                           |                           |                    |                   |         |                                               |

|----------------|----------|----------------------|------------------------|---------------------------|---------------------------|--------------------|-------------------|---------|-----------------------------------------------|

| Address        | 15       | 14                   | 13                     | 12                        | 11                        | 10                 | 9                 | 8       | Designation                                   |

| 07H<br>(Intel) | Reserved | PrmCmd_<br>Supported | Spec_Clear_<br>Mode *) | Spec_Prm_<br>Buf_Mode **) | Set_Ext_Prm<br>_Supported | User_Time_<br>Base | EOI_Time_<br>Base | DP_Mode | Mode Reg 0<br>15 8<br>See below for<br>coding |

\*) If Spec\_Clear\_Mode = 1 (Fail Safe Mode) the VPC3+C will accept Data\_Exchange telegrams without any output data (data unit length = 0) in the state DATA-EXCH. The reaction to the outputs can be parameterized in the parameterization telegram.

\*\*) When a large number of parameters have to be transmitted from the DP-Master to the DP-Slave, the Aux-Buffer 1/2 must have the same length as the Parameter-Buffer. Sometimes this could reach the limit of the available memory in the VPC3+C. When Spec\_Prm\_Buf\_Mode = 1 the parameterization data are processed directly in this special buffer and the Aux-Buffers can be held compact.

|               | Mode Register 0, Low-Byte, Address 06H (Intel):                                                                                                                                                                                                                  |

|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 7<br>rw-0 | Freeze_Supported: Freeze_Mode support<br>0 = Freeze_Mode is not supported.<br>1 = Freeze_Mode is supported                                                                                                                                                       |

| bit 6<br>rw-0 | Sync_Supported: Sync_Mode support<br>0 = Sync_Mode is not supported.<br>1 = Sync_Mode is supported.                                                                                                                                                              |

| bit 5<br>rw-0 | <ul> <li>Early_Rdy: Early Ready</li> <li>0 = Normal Ready: Ready is generated when data is valid (write) or when data has been accepted (read).</li> <li>1 = Ready is generated one clock pulse earlier</li> </ul>                                               |

| bit 4<br>rw-0 | <ul><li>INT_Pol: Interrupt Polarity</li><li>0 = The interrupt output is low-active.</li><li>1 = The interrupt output is high-active.</li></ul>                                                                                                                   |

| bit 3<br>rw-0 | <b>CS_Supported:</b> Enable Clock Synchronization<br>0 = Clock Synchronization is disabled (default)<br>1 = Clock Synchronization is enabled                                                                                                                     |

| bit 2<br>rw-0 | WD_Base: Watchdog Time Base<br>0 = Watchdog time base is 10 ms (default state)<br>1 = Watchdog time base is 1 ms                                                                                                                                                 |

| bit 1<br>rw-0 | <b>Dis_Stop_Control:</b> Disable Stopbit Control<br>0 = Stop bit monitoring is enabled.<br>1 = Stop bit monitoring is switched off<br>Set_Prm telegram overwrites this memory cell in the DP_Mode. (Refer to the<br>user specific data.)                         |

| bit 0<br>rw-0 | <pre>Dis_Start_Control: Disable Startbit Control 0 = Monitoring the following start bit is enabled. 1 = Monitoring the following start bit is switched off Set_Prm telegram overwrites this memory cell in the DP_Mode. (Refer to the user specific data.)</pre> |

Figure 5-1: Coding of Mode Register 0, Low-Byte

|                | Mode Register 0, High-Byte, Address 07H (Intel):                                                                                                                                                                    |

|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 15<br>rw-0 | Reserved                                                                                                                                                                                                            |

| bit 14<br>rw-0 | <ul> <li>PrmCmd_Supported: PrmCmd support for redundancy</li> <li>0 = PrmCmd is not supported.</li> <li>1 = PrmCmd is supported</li> </ul>                                                                          |

| bit 13<br>rw-0 | <b>Spec_Clear_Mode:</b> Special Clear Mode (Fail Safe Mode)<br>0 = No special clear mode.<br>1 = Special clear mode. VPC3+C will accept data telegrams with data unit = 0                                           |

| bit 12<br>rw-0 | <b>Spec_Prm_Buf_Mode:</b> Special-Parameter-Buffer Mode<br>0 = No Special-Parameter-Buffer.<br>1 = Special-Parameter-Buffer mode. Parameterization data will be stored<br>directly in the Special-Parameter-Buffer. |

| bit 11<br>rw-0 | Set_Ext_Prm_Supported: Set_Ext_Prm telegram support<br>0 = SAP 53 is deactivated<br>1 = SAP 53 is activated                                                                                                         |

| bit 10<br>rw-0 | <b>User_Time_Base:</b> Timebase of the cyclical User_Time_Clock-Interrupt<br>0 = The User_Time_Clock-Interrupt occurs every 1 ms.<br>1 = The User_Time_Clock-Interrupt occurs every 10 ms.                          |

| bit 9<br>rw-0  | <b>EOI_Time_Base:</b> End-of-Interrupt Timebase<br>0 = The interrupt inactive time is at least 1 μs long.<br>1 = The interrupt inactive time is at least 1 ms long                                                  |

| bit 8<br>rw-0  | <b>DP_Mode:</b> DP_Mode enable<br>0 = DP_Mode is disabled.<br>1 = DP_Mode is enabled. VPC3+C sets up all DP_SAPs (default configuration!)                                                                           |

Figure 5-2: Coding of Mode Register 0, High-Byte

#### 5.1.2 Mode Register 1

Some control bits must be changed during operation. These control bits are combined in Mode Register 1 and can be set independently of each other (Mode-Reg\_1\_S) or can be reset independently of each other (Mode-Reg\_1\_R). Separate addresses are used for setting and resetting. A logical '1' must be written to the bit position to be set or reset.

For example, to set START\_VPC3 write a '1' to address 08H, in order to reset this bit, write a '1' to address 09H.

### **5 ASIC Interface**

| Address |          |          | Designation     |                          |                       |            |     |                |                                               |

|---------|----------|----------|-----------------|--------------------------|-----------------------|------------|-----|----------------|-----------------------------------------------|

| Audress | 7        | 6        | 5               | 4                        | 3                     | 2          | 1   | 0              | Designation                                   |

| 08H     | Reserved | Reserved | Res_<br>User_WD | En_Change_<br>Cfg_Buffer | User_LEAVE-<br>MASTER | Go_Offline | EOI | START_<br>VPC3 | Mode-Reg_1_S<br>70                            |

| 09H     | Reserved | Reserved | Res_<br>User_WD | En_Change_<br>Cfg_Buffer | User_LEAVE-<br>MASTER | Go_Offline | EOI | START_<br>VPC3 | Mode-Reg_1_R<br>70<br>See below<br>for coding |

|               | Mode Register 1, Set, Address 08H:                                                                                                                                                                                                                                                                                               |

|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 7<br>rw-0 | Reserved                                                                                                                                                                                                                                                                                                                         |

| bit 6<br>rw-0 | Reserved                                                                                                                                                                                                                                                                                                                         |

| bit 5<br>rw-0 | Res_User_WD: Resetting the User_WD_Timer<br>1 = VPC3+C sets the User_WD_Timer to the parameterized value<br>User_WD_Value. After this action, VPC3+C sets Res_User_WD to '0'.                                                                                                                                                    |

| bit 4<br>rw-0 | <ul> <li>En_Change_Cfg_Buffer: Enabling buffer exchange (Config-Buffer for Read_Config-Buffer)</li> <li>0 = With User_Cfg_Data_Okay_Cmd, the Config-Buffer may not be exchanged for the Read_Config-Buffer.</li> <li>1 = With User_Cfg_Data_Okay_Cmd, the Config-Buffer must be exchanged for the Read_Config-Buffer.</li> </ul> |

| bit 3<br>rw-0 | User_LEAVE-MASTER. Request to the DP_SM to go to WAIT-PRM.<br>1 = The user causes the DP_SM to go to WAIT-PRM.<br>After this action, VPC3+ sets User_LEAVE-MASTER to '0' again.                                                                                                                                                  |

| bit 2<br>rw-0 | <ul> <li>Go_Offline: Going into the Offline state</li> <li>1 = After the current request ends, VPC3+C goes to the Offline state and sets Go_Offline to '0' again.</li> </ul>                                                                                                                                                     |

| bit 1<br>rw-0 | <b>EOI:</b> End-of-Interrupt<br>1 = VPC3+C disables the interrupt output and sets EOI to '0' again.                                                                                                                                                                                                                              |

| bit 0<br>rw-0 | <pre>Start_VPC3: Exiting the Offline state 1 = VPC3+C exits offline and goes to Passive_Idle In addition the Idle Timer and Watchdog Timer are started and 'Go_Offline = 0' is set</pre>                                                                                                                                         |

Figure 5-3: Coding of Mode Register 1

### 5.1.3 Mode Register 2

| Setting parameters for Mode Register 2 may take place in the Offline |

|----------------------------------------------------------------------|

| State only (like Mode Register 0).                                   |

| Address |          |                           |          | Designation |             |             |                          |             |                   |

|---------|----------|---------------------------|----------|-------------|-------------|-------------|--------------------------|-------------|-------------------|

| Address | 7        | 6                         | 5        | 4           | 3           | 2           | 1                        | 0           | Designation       |

|         | 0        | 0                         | 0        | 0           | 0           | 0           | 0                        | 1           | Reset Value       |

| 0CH     | 4kB_Mode | No_Check_<br>Prm_Reserved | SYNC_Pol | SYNC_Ena    | DX_Int_Port | DX_Int_Mode | No_Check_<br>GC_Reserved | GC_Int_Mode | Mode Reg 2<br>7 0 |

### **5 ASIC Interface**

|              | Mode Register 2, Address 0CH:                                                                                                                                                                                                                                                                       |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 7<br>w-0 | <b>4KB_Mode:</b> size of internal RAM<br>0 = 2K Byte RAM (default).<br>1 = 4K Byte RAM                                                                                                                                                                                                              |

| bit 6<br>w-0 | <ul> <li>No_Check_Prm_Reserved: disables checking of the reserved bits in DPV1_Status_2/3 of Set_Prm telegram</li> <li>0 = reserved bits of a Set_Prm telegram are checked (default).</li> <li>1 = reserved bits of a Set_Prm telegram are not checked.</li> </ul>                                  |

| bit 5<br>w-0 | <b>SYNC_Pol:</b> polarity of SYNC pulse (for Isochron Mode only)<br>0 = negative polarity of SYNC pulse (default)<br>1 = positive polarity of SYNC pulse                                                                                                                                            |

| bit 4<br>w-0 | <b>SYNC_Ena:</b> enables generation of SYNC pulse (for Isochron Mode only)<br>0 = SYNC pulse generation is disabled (default)<br>1 = SYNC pulse generation is enabled                                                                                                                               |

| bit 3<br>w-0 | <ul> <li>DX_Int_Port: Port mode for DX_Out interrupt (ignored if SYNC_Ena set)</li> <li>0 = DX_Out interrupt is not assigned to port DATAEXCH (default).</li> <li>1 = DX_Out Interrupt (synchronized to SYNCH telegram) is assigned to port DATAEXCH.</li> </ul>                                    |

| bit 2<br>w-0 | <ul> <li>DX_Int_Mode: Mode of DX_out interrupt</li> <li>0 = DX_Out interrupt is only generated, if Len_Dout_Buf is unequal 0 (default).</li> <li>1 = DX_Out interrupt is generated after every Data_Exchange telegram</li> </ul>                                                                    |

| bit 1<br>w-0 | <ul> <li>No_Check_GC_Reserved: Disables checking of the reserved bits in Global_Control telegram</li> <li>0 = reserved bits of a Global_Control telegram are checked (default).</li> <li>1 = reserved bits of a Global_Control telegram are not checked.</li> </ul>                                 |

| bit 0<br>w-1 | <ul> <li>GC_Int_Mode: Controls generation of New_GC_Command interrupt</li> <li>0 = New_GC_Command interrupt is only generated, if a changed<br/>Global_Control telegram is received</li> <li>1 = New_GC_Command interrupt is generated after every Global_Control<br/>telegram (default)</li> </ul> |

Figure 5-4: Coding of Mode Register 2

### 5.1.4 Mode Register 3

Setting parameters for Mode Register 3 may take place in the Offline State only (like Mode Register 0).

| Address |             |  |      | Designation |  |  |               |                  |                   |  |

|---------|-------------|--|------|-------------|--|--|---------------|------------------|-------------------|--|

| Audress | 7 6 5 4 3 2 |  |      |             |  |  |               | 0                | Designation       |  |

| 12H     |             |  | Rese | erved       |  |  | DX_Int_Mode_2 | GC_Int_Mode _Ext | Mode Reg 3<br>7 0 |  |

|              | Mode Register 3, Address 12H:                                                                                                                                                                               |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 7<br>w-0 | Reserved                                                                                                                                                                                                    |

| bit 6<br>w-0 | Reserved                                                                                                                                                                                                    |

| bit 5<br>w-0 | Reserved                                                                                                                                                                                                    |

| bit 4<br>w-0 | Reserved                                                                                                                                                                                                    |

| bit 3<br>w-0 | Reserved                                                                                                                                                                                                    |

| bit 2<br>w-0 | Reserved                                                                                                                                                                                                    |

| bit 1        | DX_Int_Mode_2: Mode of DX_out interrupt                                                                                                                                                                     |

| w-0          | <ul> <li>0 = DX_Out interrupt is generated after each Data_Exch telegram</li> <li>1 = DX_Out interrupt is only generated, if received data is not equal to current data in DX_Out buffer of user</li> </ul> |

| bit 0        | GC_Int_Mode_Ext: extend GC_Int_Mode, works only if GC_Int_Mode=0                                                                                                                                            |

| w-0          | <ul> <li>0 = GC Interrupt is only generated, if changed GC telegram is received</li> <li>1 = GC Interrupt is only generated, if GC telegram with changed<br/>Control_Command is received</li> </ul>         |

Figure 5-5: Coding of Mode Register 3

### **5 ASIC Interface**

### 5.2 Status Register

The Status Register shows the current VPC3+C status and can be read only.

| Address        |     |       | Designation |       |         |           |          |                          |                               |

|----------------|-----|-------|-------------|-------|---------|-----------|----------|--------------------------|-------------------------------|

| Address        | 7   | 6     | 6 5 4       |       | 3       | 2         | 1        | 0                        | Designation                   |

| 04H<br>(Intel) | WD_ | State | DP_3        | State | eserved | Diag_Flag | Reserved | Offline/<br>Passive_Idle | Status-Reg<br>70<br>See below |

|                | 1   | 0     | 1           | 0     | Ř       | D         | Ř        | Óå                       | for coding                    |

| Address        |               |    | Decignation |    |           |    |   |   |                         |

|----------------|---------------|----|-------------|----|-----------|----|---|---|-------------------------|

| Address        | 15            | 14 | 13          | 12 | 11        | 10 | 9 | 8 | Designation             |

| 05H<br>(Intel) | VPC3+ Release |    |             |    | Baud Rate |    |   |   | Status-Reg<br>158       |

|                | 3             | 2  | 1           | 0  | 3         | 2  | 1 | 0 | See below<br>for coding |

|                 | Status Register,Low-Byte, Address 04H (Intel):                                                                                                                                                                  |

|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 7,6<br>r-00 | WD_State 10: State of the Watchdog State Machine<br>00 = BAUD_SEARCH state<br>01 = BAUD_CONTROL state<br>10 = DP_CONTROL state<br>11 = Not possible                                                             |

| bit 5,4<br>r-00 | DP_State 10: State of the DP State Machine<br>00 = WAIT-PRM state<br>01 = WAIT-CFG state<br>10 = DATA-EXCH state<br>11 = Not possible                                                                           |

| bit 3<br>r-0    | Reserved                                                                                                                                                                                                        |

| bit 2<br>r-0    | <ul> <li>Diag_Flag: Status of the Diagnosis-Buffer</li> <li>0 = The Diagnosis-Buffer had been fetched by the DP-Master.</li> <li>1 = The Diagnosis-Buffer had not been fetched by the DP-Master yet.</li> </ul> |

| bit 1<br>r-0    | Reserved                                                                                                                                                                                                        |

| bit 0<br>r-0    | <b>Offline/Passive-Idle:</b> Offline-/Passive_Idle state<br>0 = VPC3+C is in Offline.<br>1 = VPC3+C is in Passive_Idle.                                                                                         |

Figure 5-6: Status Register, Low-Byte

|                     | Status Register, High-Byte, Address 05H (Intel):                                                                                                                                                                                                                                                                               |

|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 15-12<br>r-1100 | VPC3+-Release 30 : Release number for VPC3+<br>0000 = Step A<br>1011 = Step B<br>1100 = Step C<br>1101 = Step D<br>Rest = Not possible                                                                                                                                                                                         |

| bit 11-8<br>r-1111  | Baud Rate 30 : The baud rate found by VPC3+C<br>0000 = 12,00 Mbit/s<br>0001 = 6,00 Mbit/s<br>0010 = 3,00 Mbit/s<br>0011 = 1,50 Mbit/s<br>0100 = 500,00 Kbit/s<br>0101 = 187,50 Kbit/s<br>0111 = 45,45 Kbit/s<br>1010 = 9,20 Kbit/s<br>1001 = 9,60 Kbit/s<br>1111 = after reset and during baud rate search Rest = not possible |

Figure 5-7: Status Register, High-Byte

### 5.3 Interrupt Controller

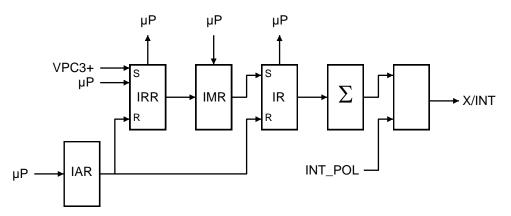

The processor is informed about indication messages and various error events via the interrupt controller. Up to a total of 16 events are stored in the interrupt controller. The events are summed up to a common interrupt output. The controller does not have a prioritization level and does not provide an interrupt vector (not 8259A compatible!).

The controller consists of an Interrupt Request Register (IRR), an Interrupt Mask Register (IMR), an Interrupt Register (IR) and an Interrupt Acknowledge Register (IAR).

Figure 5-8: Block Diagram of Interrupt Controller

Each event is stored in the IRR. Individual events can be suppressed via the IMR. The input in the IRR is independent of the interrupt masks. Events that are not masked in the IMR set the corresponding IR bit and generate the X/INT interrupt via a sum network. The user can set each event in the IRR for debugging.

Each interrupt event that was processed by the microcontroller must be deleted via the IAR (except for New\_(Ext\_)Prm\_Data and New\_Cfg\_Data). A logical '1' must be written on the specific bit position. If a new event and an acknowledge from the previous event are present at the IRR at the same time, the event remains stored. If the microcontroller enables a mask subsequently, it must be ensured that no prior IRR input is present. To be on the safe side, the position in the IRR must be deleted prior to the enabling of the mask.

Before leaving the interrupt routine, the microprocessor must set the 'end of interrupt bit' (EOI = 1) in Mode Register 1. The interrupt output is switched to inactive with this edge change. If another event occurs, the interrupt output is not activated again until the interrupt inactive time of at least 1  $\mu$ s or 1 ms expires. This interrupt inactive time can be set via EOI\_Time\_Base in Mode Register 0. This makes it possible to enter the interrupt routine again when an edge-triggered interrupt input is used.

The polarity of the interrupt output is parameterized via the Int\_Pol bit in Mode Register 0. After hardware reset, the output is low-active.

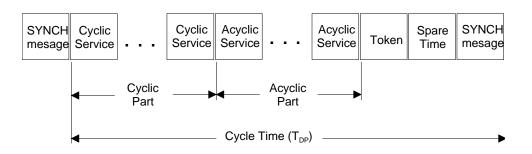

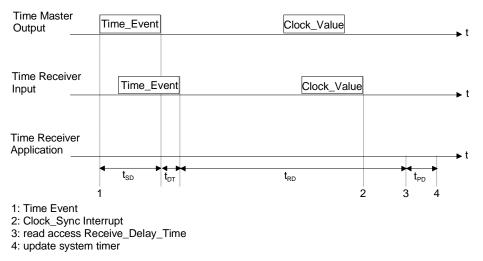

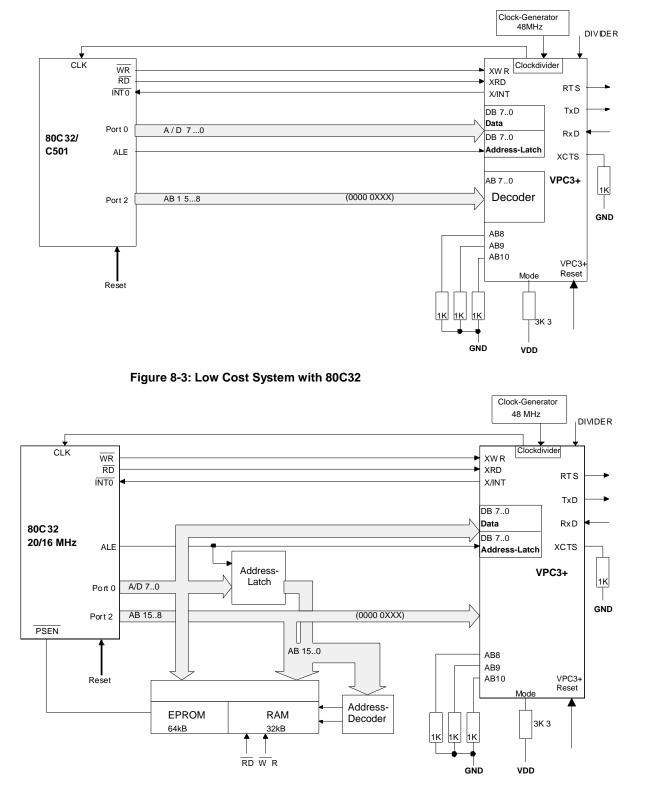

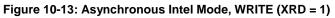

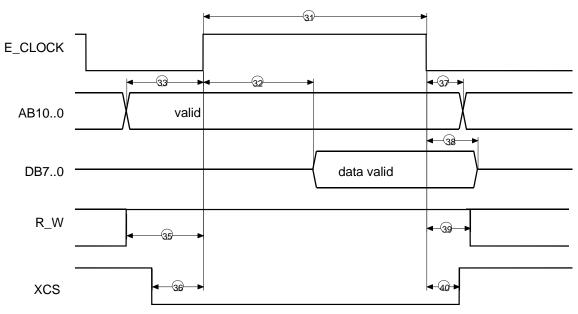

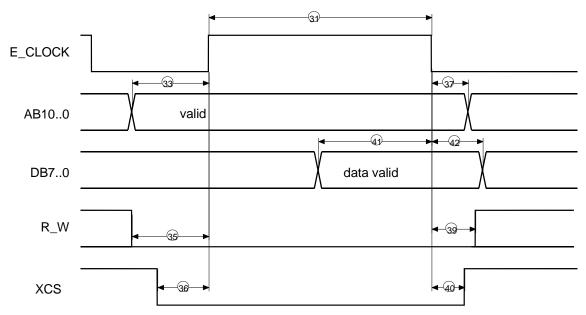

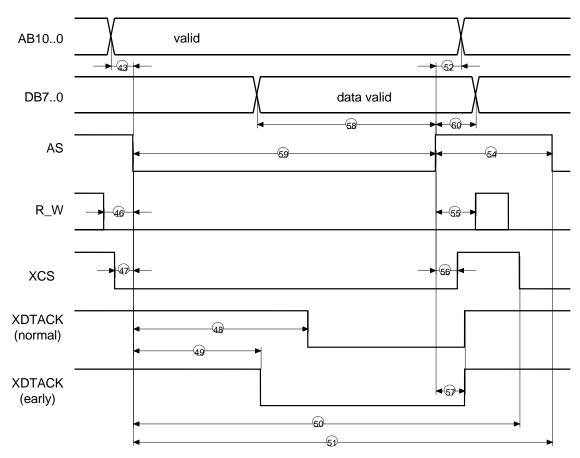

#### 5.3.1 Interrupt Request Register