# **DSTni-EX User Guide**

**Section Three**

Part Number 900-335 Revision A 3/04

# **Copyright & Trademark**

© 2003 Lantronix, Inc. All rights reserved.

Lantronix and the Lantronix logo, and combinations thereof are registered trademarks of Lantronix, Inc. DSTni is a registered trademark of Lantronix, Inc. Ethernet is a registered trademark of Xerox Corporation. All other product names, company names, logos or other designations mentioned herein are trademarks of their respective owners.

- Am186 is a trademark of Advanced Micro Devices, Inc.

- Ethernet is a registered trademark of Xerox Corporation.

- SPI is a trademark of Motorola, Inc.

No part of this guide may be reproduced or transmitted in any form for any purpose other than the purchaser's personal use, without the express written permission of Lantronix, Inc.

#### Lantronix

15353 Barranca Parkway Irvine, CA 92618, USA Phone: 949-453-3990 Fax: 949-453-3995

#### **Technical Support**

Phone: 630-245-1445 Fax: 630-245-1717

#### **Master Distributor**

Grid Connect 1841 Centre Point Circle, Suite 143 Naperville, IL 60563 Phone: 630-245-1445 www.gridconnect.com

Am186 is a trademark of Advanced Micro Devices, Inc. Ethernet is a registered trademark of Xerox Corporation. SPI is a trademark of Motorola, Inc.

| REV | Changes                                     | Released Date |

|-----|---------------------------------------------|---------------|

| A   | Reformat. Add changes from Design Spec. 1.1 | 3-24-04       |

# Contents

| Conversion 4 9 Trademont         |          |

|----------------------------------|----------|

| Copyright & Trademark            |          |

| Contents<br>List of Figures      | II<br>ii |

| List of Tables                   | iii      |

| About This User Guide            | 1        |

| Intended Audience                | 2        |

| Conventions                      | 2        |

| Navigating Online                | 2        |

| Organization                     | 3        |

| Serial Ports                     | 5        |

| Overview                         | 5        |

| Block Diagram                    |          |

| Theory of Operation              | 6        |

| Serial Port Register Summary     |          |

| Serial Port Register Definitions | 10       |

| Programmable Input/Output        | 19       |

| Overview                         | 19       |

| Theory of Operation              | 19       |

| PIO Register Summary             |          |

| PIO Register Definitions         | 21       |

| Timers                           | 25       |

| Timer Register Summary           | 25       |

| Timer Register Definitions       |          |

|                                  |          |

# List of Figures

| Figure 1. Serial Port Block Diagram | 5 |

|-------------------------------------|---|

| Figure 2. DCE/DTE Protocol          |   |

| Figure 3. CTS/RTS Protocol          | 7 |

# **List of Tables**

| Table 1. Flow Control Signals                                                                                     | 8    |

|-------------------------------------------------------------------------------------------------------------------|------|

| Table 2. Serial Port Register Summary                                                                             |      |

| Table 3. System Auxiliary Control (AUXCON) Registers                                                              | . 10 |

| Table 4. System Auxiliary Control (AUXCON) Register Definitions                                                   | . 11 |

| Table 5. FIFO Depth Settings                                                                                      |      |

| Table 6. Serial Port Baud Rate Divisor Registers                                                                  |      |

| Table 7. Serial Port Baud Rate Divisor Register Definitions                                                       | . 12 |

| Table 8. Serial Port Receive Data Registers                                                                       | .13  |

| Table 9. Serial Port Receive Data Register Definitions                                                            | . 13 |

| Table 10. Serial Port Transmit Data Registers                                                                     | .14  |

| Table 11. Serial Port Transmit Data Register Definitions                                                          |      |

| Table 12. Serial Port Status Registers                                                                            | . 15 |

| Table 13. Serial Port Status Register Definitions                                                                 |      |

| Table 14. Serial Port Control Registers                                                                           |      |

| Table 15. Serial Port Control Register Definitions                                                                | . 17 |

| Table 16. DMA Bit Settings                                                                                        | . 18 |

| Table 17. Serial Port Operating Mode Settings                                                                     | . 18 |

| Table 18. Parallel Port Functions                                                                                 |      |

| Table 19. PIO Sharing Designations                                                                                |      |

| Table 20. PIO Register Summary                                                                                    |      |

| Table 21. Parallel Port 1 Data Register                                                                           |      |

| Table 22. Parallel Port 1 Data Register Definitions                                                               |      |

| Table 23. Parallel Port 1 Direction Register                                                                      | . 22 |

| Table 24. Parallel Port 1 Direction Register Definitions                                                          |      |

| Table 25. Parallel Port 1 Mode Register                                                                           | .23  |

| Table 26. Parallel Port 1 Mode Register Definitions                                                               |      |

| Table 27. Parallel Port 0 Data Register                                                                           | .23  |

| Table 28. Parallel Port 0 Data Register Definitions                                                               |      |

| Table 29. Parallel Port 0 Direction Register                                                                      |      |

| Table 30. Parallel Port 0 Direction Register Definitions                                                          |      |

| Table 31. Parallel Port 0 Mode Register                                                                           |      |

| Table 32. Parallel Port 0 Mode Register Definitions                                                               |      |

| Table 33. Timer Register Summary                                                                                  | . 25 |

| Table 34. Watchdog Timer Control Register                                                                         |      |

| Table 35. Watchdog Timer Control Register Definitions                                                             |      |

| Table 36. Watchdog Exponent Settings                                                                              |      |

| Table 37. Watchdog Timeout Examples                                                                               |      |

| Table 38. Timer 2 Mode/Control Register                                                                           |      |

| Table 39. Timer 2 Mode/Control Register Definitions                                                               |      |

| Table 40. Max Count Compare A Register                                                                            |      |

| Table 41. Max Count Compare A Register Definitions                                                                |      |

| Table 42. Timer 2 Count Register                                                                                  | .30  |

| Table 43. Timer 2 Count Register Definitions                                                                      |      |

| Table 44. Timer 1 Mode Control Register                                                                           |      |

| Table 45. Timer 1 Mode Control Register Definitions                                                               | .31  |

| Table 46. Timer 1 Max Count Compare B Register                                                                    |      |

| Table 47. Timer 1 Max Count Compare B Register Definitions                                                        | . 33 |

| Table 48. Timer 1 Max Count Compare A Register                                                                    | . 33 |

| Table 49. Timer 1 Max Count Compare A Register Definitions                                                        |      |

| Table 50. Timer 1 Count Register         Table 51. Timer 1 Count Register Definitions                             | . 34 |

|                                                                                                                   |      |

| Table 52. Timer 0 Mode/Control Register         Table 53. Timer 0 Mode/Control Register Definitions               |      |

|                                                                                                                   |      |

| Table 54. Timer 0 Max Count Compare B Register         Table 55. Timer 0 Max Count Compare B Register Definitions |      |

| Table 55. Timer 0 Max Count Compare & Register Definitions                                                        |      |

| Table 56. Timer 0 Max Count Compare A Register Definitions                                                        | 36   |

|                                                                                                                   |      |

| Lable 58 Limer II Count Redister                                                                                  |      |

| Table 58. Timer 0 Count Register         Table 59. Timer 0 Count Register Definitions                             | . 37 |

# About This User Guide

This User Guide describes the technical features and programming interfaces of the Lantronix DSTni-EX chip (hereafter referred to as "DSTni").

DSTni is an Application Specific Integrated Circuit (ASIC)-based single-chip solution (SCS) that integrates the leading-edge functionalities needed to develop low-cost, high-performance device server products. On a single chip, the DSTni integrates an x186 microprocessor, 16K-byte ROM, 256K-byte SRAM, programmable input/output (I/O), and serial, Ethernet, and Universal Serial Bus (USB) connectivity — key ingredients for device- server solutions. Although DSTni embeds multiple functions onto a single chip, it can be easily customized, based on the comprehensive feature set designed into the chip.

Providing a complete device server solution on a single chip enables system designers to build affordable, full-function solutions that provide the highest level of performance in both processing power and peripheral systems, while reducing the number of total system components. The advantages gained from this synergy include:

- Simplifying system design and increased reliability.

- Minimizing marketing and administration costs by eliminating the need to source products from multiple vendors.

- Eliminating the compatibility and reliability problems that occur when combining separate subsystems.

- Dramatically reducing implementation costs.

- Increasing performance and functionality, while maintaining quality and cost effectiveness.

- Streamlining development by reducing programming effort and debugging time.

- Enabling solution providers to bring their products to market faster.

These advantages make DSTni the ideal solution for designs requiring x86 compatibility; increased performance; serial, programmable I/O, Ethernet, and USB communications; and a glueless bus interface.

### **Intended Audience**

This User Guide is intended for use by hardware and software engineers, programmers, and designers who understand the basic operating principles of microprocessors and their systems and are considering designing systems that utilize DSTni.

# **Conventions**

This User Guide uses the following conventions to alert you to information of special interest.

The symbols # and n are used throughout this Guide to denote active LOW signals.

Notes: Notes are information requiring attention.

# **Navigating Online**

The electronic Portable Document Format (PDF) version of this User Guide contains <u>hyperlinks</u>. Clicking one of these hyper links moves you to that location in this User Guide. The PDF file was created with Bookmarks and active links for the Table of Contents, Tables, Figures and cross-references.

# Organization

This User Guide contains information essential for system architects and design engineers. The information in this User Guide is organized into the following chapters and appendixes.

- <u>Section 1: Introduction</u>

Describes the DSTni architecture, design benefits, theory of operations, ball assignments, packaging, and electrical specifications. This chapter includes a DSTni block diagram.

- <u>Section 2: Microprocessor</u>

Describes the DSTni microprocessor and its control registers.

- <u>Section 2: SDRAM</u>

Describes the DSTni SDRAM and the registers associated with it.

- <u>Section 3: Serial Ports</u>

Describes the DSTni serial ports and the registers associated with them.

- <u>Section 3: Programmable Input/Output</u>

Describes DSTni's Programmable Input/ Output (PIO) functions and the registers associated with them.

- <u>Section 3: Timers</u>

Describes the DSTni timers.

- <u>Section 4: Ethernet Controllers</u> Describes the DSTni Ethernet controllers.

- <u>Section 4: Ethernet PHY</u>

Describes the DSTni Ethernet physical layer core.

- <u>Section 5: SPI Controller</u>

Describes the DSTni Serial Peripheral Interface (SPI) controller.

- <u>Section 5: I2C Controller</u> Describes the DSTni I<sup>2</sup>C controller.

- <u>Section 5: USB Controller</u> Describes the DSTni USB controller.

- <u>Section 5: CAN Controllers</u>

Describes the DSTni Controller Area Network (CAN) bus controllers.

- <u>Section 6: Interrupt Controller</u> Describes the DSTni interrupt controller.

- <u>Section 6: Miscellaneous Registers</u> Describes DSTni registers not covered in other chapters of this Guide.

- <u>Section 6: Debugging In-circuit Emulator (Delce)</u>

- <u>Section 6: Packaging and Electrical</u> Describes DSTni's packaging and electrical characteristics.

- <u>Section 6: Applications</u> Describes DSTni's packaging and electrical characteristics.

- <u>Section 6: Instruction Clocks</u>

Describes the DSTni instruction clocks.

- <u>Section 6: DSTni Sample Code</u>

- <u>Section 6: Baud Rate Calculations</u>

Provides baud rate calculation tables.

# **Serial Ports**

**Block Diagram**

# **Overview**

This chapter describes the DSTni serial ports and the registers associated with them. Topics include:

- Block Diagram on page 5

- Theory of Operation on page 6

- Serial Port Register Summary on page 9

- Serial Port Register Definitions on page 10

- ٠

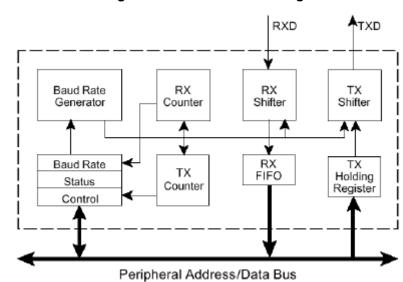

#### Figure 1. Serial Port Block Diagram

# Theory of Operation

#### Features

DSTni provides four dentical asynchronous serial ports (see Figure 1). Each port operates independently and provides the following features:

- A read port and a write port for full-duplex operation with a programmable baudrate generator.

- Supports 7-, 8-, and 9-bit operation, with even, odd, or no parity and one or two stop bits.

- Ability to transmit and detect break characters. Receive port can be programmed to generate interrupts when a break character is sent or received. It can also be programmed to generate interrupts when the next word of data can be sent or a valid word of data is received.

- Serial ports can be configured to use Direct Memory Access (DMA) for data transmission, reception, or both.

#### **Flow Control**

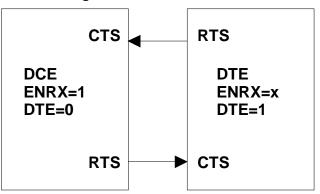

The DSTni serial ports support two hardware flow control protocols: DCE/DTE and Clear To Send/Ready To Receive (CTS/RTS). The hardware flow control protocol is selected using the ENRX and DTE bits in the System Auxiliary Control (AUXCON) register.

#### **DCE/DTE Protocol**

With the DCE/DTE protocol, the serial port is configured as either a Data Communication Equipment (DCE) or Data Terminal Equipment (DTE) device (see Figure 2).

- As a DTE device, the chip sends a Request To Send (RTS) when data is waiting to be sent. Then the DTE device waits for a CTS from the DCE device before it sends the frame.

- As a DCE device, the serial port receives a request to enable receiver (ENRX) from the DTE device. It then responds with an RTS signal.

To configure a serial port as a DTE device:

- Set both the associated DTE bit and the associated ENRX bit. The DTE and ENRX bits for both serial ports can be found in the System Auxiliary Control (AUXCON) register.

- Enable flow control by setting the FC bit in the Serial Port Control register.

#### Figure 2. DCE/DTE Protocol

Asymmetrical

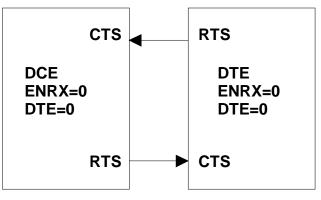

### CTS/RTR Protocol

The Clear To Send/Ready To Receive (CTS/RTR) protocol supports full-duplex operation. When a device can receive data, it asserts the ready to receive output. A device with data to be sent waits for the Clear To Send input to be asserted before it sends the data. Figure 3. CTS/RTS Protocol show this protocol.

To configure a serial port to use the Clear To Send/Ready To Receive protocol:

- Clear both the ENRX and DTE for the associated serial port. The DTE and ENRX bits for both serial ports can be found in the System Auxiliary Control (AUXCON) register.

- Enable flow control by setting the FC bit in the Serial Port Control register.

Figure 3. CTS/RTS Protocol

Symmetrical

#### **Flow Control Signals**

Table 1 lists the flow control signals for the DSTni serial ports. It also shows the register settings associated with the flow control signals.

| Flow<br>Control<br>Signal | Register Settings                                                                                    | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|---------------------------|------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RTSx                      | Auxiliary Configuration Register<br>RTS bit = 1<br>Serial Port Configuration Register<br>FC bit = 1  | Provides the RTS signal for the corresponding asynchronous serial port. The RTS signal is asserted when the associated Serial Port Transmit register contains data to transmit.                                                                                                                                                                                                                                                                                 |

| RTRx                      | Auxiliary Configuration Register<br>RTS bit = 0<br>Serial Port Configuration Register<br>FC bit = 1  | Provides the RTR signal for the corresponding asynchronous serial port. The RTR signal is asserted when the associated Serial Port Receive register and FIFO do not contain data.                                                                                                                                                                                                                                                                               |

| CTSx                      | Auxiliary Configuration Register<br>ENRX bit = 0<br>Serial Port Configuration Register<br>FC bit = 1 | Provides the CTS signal for the corresponding asynchronous<br>serial port. The CTS signal gates the transmission of data from<br>the associated Serial Port Transmit register. When CTS is<br>asserted, the transmitter transmits a frame of data, if any is<br>available. If CTS is deasserted, the transmitter holds the data in<br>the Serial Port Transmit register. The value of CTS is checked<br>only at the beginning of the transmission of the frame. |

| ENRXx                     | Auxiliary Configuration Register<br>ENRX bit = 1<br>Serial Port Configuration Register<br>FC bit = 1 | Provides the Enable Receiver Request for the corresponding asynchronous serial port. The ENRX signal enables the receiver for the associated serial port.                                                                                                                                                                                                                                                                                                       |

### **Data Transmission**

To transmit a frame, the data is written to an empty Transmit Holding register. When the Transmit Shift register is empty, the frame transfers from the Holding register to the shift register, freeing the Holding register for the data for the next frame. In this way, the data for the next frame can be written while the previous frame is transmitting. The software can poll the Transmit Holding register empty bit in the Status register, or the asynchronous serial port can be configured to generate an interrupt when the Holding register becomes empty.

To minimize data-overrun errors, the receive side of the serial port contains a 4-word receive FIFO. When a frame is received, the data and error bits for that frame are placed in the FIFO and the data-ready bit in the Status register is asserted. Three more frames can be received and stored in the FIFO before data is lost, causing the data overrun error bit to be set. Even at high baud rates, this gives the software (or DMA) ample time to read the data before an overrun error occurs. If a fifth word of data is received before any data is read from the FIFO, the oldest data in the FIFO is overwritten and the overrun error bit in the Status register will be set. When the FIFO is empty, the data ready bit in the Status register clears.

#### **DMA Transfers via Serial Ports**

DSTni supports DMA transfers both to and from the serial ports. Any or all DMA channels and any or all serial ports can be used for DMA transmits or receives.

# Serial Port Register Summary

Table 2 lists the programmable registers associated with the DSTni serial ports. The four DSTni Universal Asynchronous Receivers/Transmitters (UARTs) are similar, except as noted in the following sections. They are located at the following locations:

- SP0=80-8A

- SP1=10-1A

- SP2=00-0A

- SP3=E0-EA

#### Table 2. Serial Port Register Summary

| Hex Offset    | Mnemonic | Register Description                     | Page |

|---------------|----------|------------------------------------------|------|

| Serial Port 0 |          |                                          |      |

| 8E            | ///      | ///                                      | ///  |

| 8C            |          | ///                                      | ///  |

| 8A            | SP0CNTRL | Serial Port 0 Auxiliary Control Register | 10   |

| 88            | SP0BAUD  | Serial Port 0 Baud Rate Divisor Register | 11   |

| 86            | SP0RD    | Serial Port 0 Receive Data Register      | 13   |

| 84            | SP0TD    | Serial Port 0 Transmit Data Register     | 14   |

| 82            | SP0STS   | Serial Port 0 Status Register            | 15   |

| 80            | SP0CT    | Serial Port 0 Control Register           | 17   |

| Serial Port 1 |          |                                          |      |

| 1E            | ///      | ///                                      | ///  |

| 1C            | ///      | ///                                      | ///  |

| 1A            | SP1CNTRL | Serial Port 1 Auxiliary Control Register | 10   |

| 18            | SP1BAUD  | Serial Port 1 Baud Rate Divisor Register | 11   |

| 16            | SP1RD    | Serial Port 1 Receive Data Register      | 13   |

| 14            | SP1TD    | Serial Port 1 Transmit Data Register     | 14   |

| 12            | SP1STS   | Serial Port 1 Status Register            | 15   |

| 10            | SP1CT    | Serial Port 1 Control Register           | 17   |

| Serial Port 2 |          |                                          |      |

| 0E            | ///      | ///                                      | ///  |

| 0C            | ///      |                                          | ///  |

| 0A            | SP2CNTRL | Serial Port 2 Auxiliary Control Register | 10   |

| 08            | SP2BAUD  | Serial Port 2 Baud Rate Divisor Register | 11   |

| 06            | SP2RD    | Serial Port 2 Receive Data Register      | 13   |

| 04            | SP2TD    | Serial Port 2 Transmit Data Register     | 14   |

| 02            | SP2STS   | Serial Port 2 Status Register            | 15   |

| 00            | SP2CT    | Serial Port 2 Control Register           | 17   |

| Serial Port 3 |          |                                          |      |

| EE            | ///      |                                          | ///  |

| EC            | ///      | ///                                      | ///  |

| EA            | SP3CNTRL | Serial Port 3 Auxiliary Control Register | 10   |

| E8            | SP3BAUD  | Serial Port 3 Baud Rate Divisor Register | 11   |

| E6            | SP2RD    | Serial Port 3 Receive Data Register      | 13   |

| E4            | SP3TD    | Serial Port 3 Transmit Data Register     | 14   |

| E2            | SP3STS   | Serial Port 3 Status Register            | 15   |

| E0            | SP3CT    | Serial Port 3 Control Register           | 17   |

# **Serial Port Register Definitions**

The following sections provide the serial port register definitions. In these sections, the initialization value shown is the register's initialization value at reset.

### System Auxiliary Control (AUXCON) registers

The System Auxiliary Control (AUXCON) registers control both the transmit and receive sections of the serial ports.

*Note:* The RTSZ, RTSF, RXM, CTSM, and RTSP bits manipulate the handshake capability of each serial port.

| BIT    | 15 | 14                                         | 13 | 12 | 11  | 10 | 9    | 8 | 7    | 6   | 5  | 4  | 3      | 2   | 1  | 0    |

|--------|----|--------------------------------------------|----|----|-----|----|------|---|------|-----|----|----|--------|-----|----|------|

| OFFSET |    | Serial Port 0 = 8Ah                        |    |    |     |    |      |   |      |     |    |    |        |     |    |      |

|        |    | Serial Port 1 = 1Ah                        |    |    |     |    |      |   |      |     |    |    |        |     |    |      |

|        |    | Serial Port 2 = 0Ah<br>Serial Port 3 = EAh |    |    |     |    |      |   |      |     |    |    |        |     |    |      |

| FIELD  |    |                                            |    |    |     |    | Oena |   |      |     |    |    |        |     |    |      |

|        |    |                                            |    |    | /// |    |      |   | BRGO | FIF | OD | SZ | ц<br>С | Σ   | SM | RTSP |

|        |    |                                            |    |    |     |    |      |   | BR   |     | 0D | RT | RT     | RXM | СТ | RT   |

| RESET  | 0  | 0                                          | 0  | 0  | 0   | 0  | 0    | 0 | 0    | 1   | 0  | 0  | 0      | 0   | 0  | 0    |

| RW     | R  | R                                          | R  | R  | R   | R  | R    | R | RW   | R   | RW | R  | R      | R   | R  | R    |

|        |    |                                            |    |    |     |    |      |   |      | W   |    | W  | W      | W   | W  | W    |

#### Table 3. System Auxiliary Control (AUXCON) Registers

| Bits | Field Name | Description                                                                                                                                                                                                                                                                                                                                                              |

|------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15:8 | ///        | Reserved                                                                                                                                                                                                                                                                                                                                                                 |

| 7    | BRGO       | Baud Rate Generator Output         1 = the corresponding RTS output connects to the baud rate generator output. The output signal will be 50% duty cycle if the baud rate is even. The duty cycle will be uneven by one clock if the baud rate is odd.         Note: Baud Rate Generator Output cannot be used if the rate generator is using a count of 0000h or 0001h. |

| 6:5  | FIFOD      | <b>FIFO Depth</b><br>These 2 bits set the FIFO depth (that is, the level at which the RTS is considered full.<br>Values are from 1 to 4, default is 4. See Table 5.                                                                                                                                                                                                      |

| 4    | RTSZ       | Ready to Send Zero         This bit allows the state of the RTS pin to be masked.         1 = RTS output is forced inactive.         0 = RTS output functions normally.                                                                                                                                                                                                  |

| 3    | RTSF       | Ready To Send Force         This bit provides control over the state of the RTS pin.         1 = RTS output is forced active.         0 = RTS output functions normally.                                                                                                                                                                                                 |

| 2    | RXM        | Receiver Mask         1 = serial port is placed in half-duplex mode.         0 = serial port is in full-duplex mode, and the serial port receiver input is from the normal RXD pin.         The receive input will be read as '0'.                                                                                                                                       |

| 1    | CTSM       | CTS Mask<br>1 = serial port CTS input is read inactive.<br>0 = serial port CTS input is from the normal CTS input pin.                                                                                                                                                                                                                                                   |

| 0    | RTSP       | <b>RTS Polarity</b><br>1 = RTS signal is inverted on the RTS pin.<br>0 = RTS signal is not inverted. This permits the RTS pin to control the TXEN pin of RS-485 drivers.                                                                                                                                                                                                 |

Table 4. System Auxiliary Control (AUXCON) Register Definitions

#### Table 5. FIFO Depth Settings

| Bit [6] | Bit [5] | FIFO Depth  |

|---------|---------|-------------|

| 0       | 0       | 1           |

| 0       | 1       | 2           |

| 1       | 0       | 3 (default) |

| 1       | 1       | 4           |

### Serial Port Baud Rate Divisor Registers

All four asynchronous serial ports have a Baud Rate Divisor (BRD) register that allows the ports to operate at different rates. These registers specify a clock divisor for generating the serial clock that controls the associated serial port.

A general formula for the BRD is:

BRD = CPUCLK ÷ 16 ÷ BAUDRATE

The serial port receiver tolerates an overspeed baud rate deviation of 3.0% and an underspeed baud rate deviation of 2.5%. To help with your calculations, see Appendix B: Baud Rate Calculations for valid and invalid baud rate calculations at various microprocessor speeds.

#### SCS100/200/400 User Guide

| BIT    | 15                  | 14 | 13 | 12 | 11 | 10 | 9  | 8   | 7        | 6 | 5  | 4 | 3 | 2 | 1 | 0 |

|--------|---------------------|----|----|----|----|----|----|-----|----------|---|----|---|---|---|---|---|

| OFFSET | Serial Port 0 = 88h |    |    |    |    |    |    |     |          |   |    |   |   |   |   |   |

|        | Serial Port 1 = 18h |    |    |    |    |    |    |     |          |   |    |   |   |   |   |   |

|        | Serial Port 2 = 08h |    |    |    |    |    |    |     |          |   |    |   |   |   |   |   |

|        | Serial Port 3 = E8h |    |    |    |    |    |    |     |          |   |    |   |   |   |   |   |

| FIELD  |                     |    |    |    |    |    |    | BR  | <b>`</b> |   |    |   |   |   |   |   |

|        |                     |    |    |    |    |    |    | DRI | <u> </u> |   |    |   |   |   |   |   |

| RESET  | 0                   | 0  | 0  | 0  | 0  | 0  | 0  | 0   | 0        | 0 | 0  | 0 | 1 | 1 | 0 | 1 |

| RW     | RW                  | R  | R  | RW | RW | RW | RW | R   | RW       | R | RW | R | R | R | R | R |

|        |                     | W  | W  |    |    |    |    | W   |          | W |    | W | W | W | W | W |

#### Table 6. Serial Port Baud Rate Divisor Registers

| Bits | Field Name | Description                                                                                                                                                        |

|------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15:0 | BRD        | <b>Baud Rate Divisor</b><br>By setting the baud rate divisor to 0, the maximum baud rate for a given<br>frequency (frequency/16) can be achieved (UART Clock/BRD). |

### Serial Port Receive Data Registers

The Serial Port Receive registers are Read Only registers that contain data received over the serial ports. The receiver is double-buffered; consequently, the receive section can be receiving a subsequent frame of data in the Receive Shift register, which is not accessible to software, while the Receive Data register is being read.

The Receive Data Ready (RDR) bit in the Serial Port Status register reports the current state of this register (see page 15). When the RDR bit is 1, the Receive register contains valid unread data. The RDR bit clears automatically when the Receive register is read.

If hardware handshaking is enabled, the CTS/ENRX signals are deasserted while the Receive register contains valid unread data. Reading the Receive register asserts the CTS/ENRX signals. This behavior prevents overrun errors, but can cause delays in character transmissions.

| BIT    | 15 | 14                  | 13 | 12 | 11 | 10 | 9      | 8      | 7     | 6 | 5 | 4  | 3   | 2 | 1 | 0 |

|--------|----|---------------------|----|----|----|----|--------|--------|-------|---|---|----|-----|---|---|---|

| OFFSET |    | Serial Port 0 = 86h |    |    |    |    |        |        |       |   |   |    |     |   |   |   |

|        |    | Serial Port 1 = 16h |    |    |    |    |        |        |       |   |   |    |     |   |   |   |

|        |    | Serial Port 2 = 06h |    |    |    |    |        |        |       |   |   |    |     |   |   |   |

|        |    |                     |    |    |    |    | Serial | Port 3 | = E6h |   |   |    |     |   |   |   |

| FIELD  |    |                     |    | 1  | // |    |        |        |       |   |   | Da | ata |   |   |   |

|        |    |                     |    |    | 1  |    |        |        | Data  |   |   |    |     |   |   |   |

| RESET  | 0  | 0                   | 0  | 0  | 0  | 0  | 0      | 0      | 0     | 0 | 0 | 0  | 0   | 0 | 0 | 0 |

| RW     | R  | R                   | R  | R  | R  | R  | R      | R      | R     | R | R | R  | R   | R | R | R |

#### Table 8. Serial Port Receive Data Registers

#### Table 9. Serial Port Receive Data Register Definitions

| Bits | Field Name | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15:8 | ///        | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 7:0  | Data       | <b>Received Data</b><br>After all data bits are received, and the data word has been checked for framing and<br>parity errors, the data word is written to the receive data FIFO. The receive data ready<br>bit in the Status register indicates that data is ready and has been transferred to the<br>receive data FIFO. If another word is received after the FIFO is full and before this<br>FIFO is read, the overrun error bit in the Status register is set. |

#### Serial Port Transmit Data Registers

Each Transmit register is written by software with the value to be transmitted over the corresponding serial interface. The transmitter is double-buffered; consequently, before data is transmitted, it is copied from the Transmit register to the Transmit Shift register, which is not accessible to software. The state of the transmit and Transmit Shift registers is reflected in the TEMT and THRE bits for the associated Serial Port Status registers (see page 15).

If hardware handshaking is enabled, the transmitter does not transmit data while RTS/RTR inputs are deasserted. Data is held in the Transmit and Transmit Shift registers without affecting the transmit pin.

| BIT    | 15                                         | 14                  | 13 | 12 | 11  | 10 | 9   | 8       | 7       | 6  | 5  | 4  | 3  | 2  | 1  | 0  |

|--------|--------------------------------------------|---------------------|----|----|-----|----|-----|---------|---------|----|----|----|----|----|----|----|

| OFFSET |                                            | Serial Port 0 = 84h |    |    |     |    |     |         |         |    |    |    |    |    |    |    |

|        |                                            | Serial Port 1 = 14h |    |    |     |    |     |         |         |    |    |    |    |    |    |    |

|        | Serial Port 2 = 04h<br>Serial Port 3 = E4h |                     |    |    |     |    |     |         |         |    |    |    |    |    |    |    |

|        |                                            |                     |    |    |     |    | Ser | ial Por | t 3 = E | 4h |    |    |    |    |    |    |

| FIELD  |                                            |                     |    |    | /// |    |     |         | Data    |    |    |    |    |    |    |    |

| RESET  | 0                                          | 0                   | 0  | 0  | 0   | 0  | 0   | 0       | 0       | 0  | 0  | 0  | 0  | 0  | 0  | 0  |

| RW     | R                                          | R                   | R  | R  | R   | R  | R   | R       | RW      | RW | RW | RW | RW | RW | RW | RW |

#### Table 10. Serial Port Transmit Data Registers

#### Table 11. Serial Port Transmit Data Register Definitions

| Bits | Field Name | Description                                                                                                                                                                                                                        |

|------|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15:8 | ///        | Reserved                                                                                                                                                                                                                           |

| 7:0  | Data       | <b>Data to be Transmitted</b><br>Before the data can be written, the Transmit Holding Register Empty bit in the Serial<br>Port Status register must be HIGH (see page 15); otherwise, the previous word of<br>data is overwritten. |

### Serial Port Status Registers

The Serial Port Status registers provide information about the current status of the associated serial ports.

- The THRE and TEMT bits provide the software with information about the state of the transmitter.

- The BRK1, BRK0, RDR, FER, OER, and PER bits provide the software with information about the receiver.

- The HS0 bit reflects the value of the serial port's associated CTS signal.

The THRE, TEMT, and HS0 bits are updated during each microprocessor cycle.

The receive logic carries the framing error (FER), parity error (PER) and received character through the 4-deep FIFO. All the other bits set immediately.

| BIT    | 15                  | 14                  | 13  | 12 | 11 | 10   | 9     | 8       | 7             | 6   | 5  | 4   | 3   | 2    | 1   | 0  |

|--------|---------------------|---------------------|-----|----|----|------|-------|---------|---------------|-----|----|-----|-----|------|-----|----|

| OFFSET |                     | Serial Port 0 = 82h |     |    |    |      |       |         |               |     |    |     |     |      |     |    |

|        | Serial Port 1 = 12h |                     |     |    |    |      |       |         |               |     |    |     |     |      |     |    |

|        |                     | Serial Port 2 = 02h |     |    |    |      |       |         |               |     |    |     |     |      |     |    |

|        |                     |                     |     |    |    |      | Seria | al Port | <u>3 = E2</u> | h   |    |     |     |      |     |    |

| FIELD  |                     |                     |     |    |    |      |       |         |               |     |    |     |     |      |     |    |

|        |                     |                     |     |    |    | Σ.   | 9     |         | ~             | Щ   |    | ~   | ~   | Ţ    | _   | // |

|        |                     |                     | /// |    |    | BRK1 | BRKO  | RB8     | RDR           | HRE | ER | OER | PER | темт | HSO | /  |

|        |                     |                     |     |    |    | В    | В     | 22      | Ř             | H   | ш  | 0   | ٩.  | F    | I   |    |

| RESET  | 0                   | 0                   | 0   | 0  | 0  | 0    | 0     | 0       | 0             | 0   | 0  | 1   | 0   | 0    | 0   | 0  |

| RW     | R                   | R                   | R   | R  | R  | RW   | RW    | RW      | R             | R   | R  | R   | R   | R    | R   | R  |

|        |                     |                     |     |    |    |      |       |         |               |     | W  | W   | W   |      |     |    |

#### **Table 12. Serial Port Status Registers**

#### SCS100/200/400 User Guide

| Bits  | Field Name | Description                                                                                                                                                                                                                                                                                                                                                                                                                 |

|-------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15:11 | //         | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 10    | BRK1       | Long Break Detected<br>This bit sets when a long break has been detected. A long break is defined as a '0'<br>signal on the RXD pin for more than 2M+3 bit times.<br>M = StartBit + #DataBits = ParityBit + StopBits<br>To guarantee the reception of a break character it must not start in the middle of a<br>frame, it must start outside of a frame. This bit must be cleared by software.                              |

| 9     | BRK0       | Short Break Detected<br>This bit sets when a short break has been detected. A short break is defined as a '0'<br>signal on the RXD pin for more than M bit times. In order to guarantee the reception of<br>a break character it must not start in the middle of a frame, it must start outside of a<br>frame. This bit must be cleared by software.                                                                        |

| 8     | RB8        | Receive Bit 8<br>This is the ninth data bit received in modes 2 and 3. This bit must be cleared by software.                                                                                                                                                                                                                                                                                                                |

| 7     | RDR        | <b>Receive Data Ready</b><br>This Read Only bit sets when a valid word of data is transferred to the receive data<br>FIFO. When the receive FIFO becomes empty, this bit is automatically reset. The<br>serial port can be configured to generate interrupts whenever this bit is set by the<br>RXIE bit in the Serial Port Control register (see page 17).                                                                 |

| 6     | THRE       | <b>Transmit Holding Register Empty</b><br>This Read Only bit sets when a new word of data can be written to the Transmit<br>Holding register. The bit is automatically reset when the Transmit Holding register is<br>written. The serial port can be configured to generate interrupts when THRE is set by<br>setting the TXIE bit in the Serial Port Control register to 1 (see page 17) and enabling<br>the transmitter. |

| 5     | FER        | Framing Error<br>This bit indicates that a framing error has occurred. If receive status interrupts are<br>enabled (RSIE bit in Serial Port Control register, see page 17) an interrupt is<br>generated when this bit is set. The FER bit must be reset by the software.                                                                                                                                                    |

| 4     | OER        | <b>Overrun Error</b><br>This bit is set if a word in the Receive Holding register was overwritten. If receive status interrupts are enabled (RSIE bit in Control register) an interrupt is generated when this bit is set. The OER bit must be reset by the software.                                                                                                                                                       |

| 3     | PER        | <b>Parity Error</b><br>This bit indicates that a parity error has occurred. If receive status interrupts are<br>enabled (RSIE bit in Control register) an interrupt is generated when this bit is set. The<br>PER bit must be reset by the software.                                                                                                                                                                        |

| 2     | TEMT       | <b>Transmit Empty</b><br>This Read Only bit indicates that both the Transmit Holding register and Transmit Shift register are empty. When this bit is HIGH, it is safe to disable the transmitter.                                                                                                                                                                                                                          |

| 1     | HS0        | Handshake Signal 0<br>This Read Only bit reflects the value of the CTS pin (inverted). This bit is masked by<br>the CTSM bit in the System Auxiliary Control (AUXCON) register (see page 10).                                                                                                                                                                                                                               |

| 0     | ///        | Reserved<br>This Read Only bit is always 0.                                                                                                                                                                                                                                                                                                                                                                                 |

# Serial Port Control Registers

| BIT    | 15 | 14                  | 13 | 12  | 11 | 10 | 9           | 8      | 7      | 6    | 5    | 4      | 3 | 2 | 1    | 0  |

|--------|----|---------------------|----|-----|----|----|-------------|--------|--------|------|------|--------|---|---|------|----|

| OFFSET |    |                     |    |     |    |    | Seria       | Port ( | 0 = 80 | h    |      |        |   |   |      |    |

|        |    |                     |    |     |    |    |             |        | 1 = 10 |      |      |        |   |   |      |    |

|        |    | Serial Port 2 = 00h |    |     |    |    |             |        |        |      |      |        |   |   |      |    |

|        |    |                     |    |     |    |    | Seria       | Port 3 | 3 = E0 | h    |      |        |   |   |      |    |

| FIELD  |    |                     |    |     |    |    |             |        |        | 0    | Δ    |        |   |   |      |    |

|        |    | DMA                 |    | Щ   | BR | B8 |             | ш      | RXIE   | ō    | RMOD | N<br>N |   |   | MODE | =  |

|        |    |                     |    | RSI | K  | TB | U<br>L<br>L | TXIE   | X<br>X | TMOD | RN   | Ъ      | Ц |   | -    |    |

|        |    | -                   |    |     | -  |    | -           |        |        |      | -    |        | - | - |      |    |

| RESET  | 0  | 0                   | 0  | 0   | 0  | 0  | 0           | 0      | 0      | 0    | 0    | 0      | 0 | 0 | 0    | 0  |

| RW     | R  | RW                  | RW | RW  | RW | RW | RW          | R      | R      | R    | R    | R      | R | R | R    | RW |

|        | W  |                     |    |     |    |    |             | W      | W      | W    | W    | W      | W | W | W    |    |

### Table 14. Serial Port Control Registers

### Table 15. Serial Port Control Register Definitions

| Bits  | Field Name | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|-------|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15:13 | DMA        | <b>Direct Memory Access</b><br>These bits configure the serial port for use with DMA according to Table 16 on page<br>18. DMA transfers to a serial port are destination synchronized. When the Transmit<br>Holding register is empty, a new transmit is requested. When configured for transmit<br>DMA, transmit interrupts are disabled regardless of the setting of the of TXIE bit. DMA<br>transfers from the serial port (receive DMA) are source synchronized. A new transfer<br>is requested when data is available in the receive FIFO. When a serial port is<br>configured for receive DMA, receive interrupts are disabled regardless of the setting of<br>the RXIE bit. However, receive status interrupts can still be enabled. |

| 12    | RSIE       | <ul> <li>Receive Status Interrupt Enable</li> <li>1 = serial port generates an interrupt when it detects a break, parity, framing, or overrun error.</li> <li>0 = no interrupt is generated.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 11    | BRK        | Send Break Enable<br>1 = serial port generates a '0' on the TXD output.<br>0 = no break is generated.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 10    | TB8        | <b>Transmit Bit 8</b><br>In modes with nine data bits, this bit is transferred as the ninth data bit. This bit is cleared after a frame is transmitted. This bit must be set after the TEMT bit (bit [2] of the Serial Port Status register, page 15) is set.                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 9     | FC         | Flow Control Enable<br>This bit enables hardware flow control. The type of flow control used is set by the<br>System Auxiliary Control (AUXCON) register (see page 10) and the AUXCON register<br>(see page Error! Bookmark not defined.).<br>1 = flow control enabled.<br>0 = flow control disabled.                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 8     | TXIE       | <b>Transmit Holding Register Empty Interrupt Enable</b><br>1 = Transmit Holding register generates an interrupt when it goes empty.<br>0 = Transmit Holding register does not generate interrupt when it goes empty.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 7     | RXIE       | Receive Data Ready Interrupt Enable1 = Receive Data register generates an interrupt when a valid word is received.0 = Receive Data register does not generate interrupt when a valid word is received.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 6     | TMOD       | Transmit Mode Enable1 = transmitter is enabled.0 = transmitter will be disabled.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 5     | RMOD       | Receive Mode Enable1 = receiver is enabled.0 = receiver will be disabled.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

#### SCS100/200/400 User Guide

| Bits | Field Name | Description                                                                               |

|------|------------|-------------------------------------------------------------------------------------------|

| 4    | EVN        | Even Parity                                                                               |

|      |            | If parity is enabled:                                                                     |

|      |            | 1 = even parity generation and checking.                                                  |

|      |            | 0 = odd parity generation and checking.                                                   |

| 3    | PE         | Parity Enable                                                                             |

|      |            | 1 = enables the serial port to insert a parity bit into each data character and check for |

|      |            | the appropriate parity for each received data character.                                  |

|      |            | 0 = disables parity generation and checking.                                              |

| 2:0  | MODE       | Operating Mode                                                                            |

|      |            | Determines the operating mode for the serial port. See Table 17.                          |

#### Table 16. DMA Bit Settings

|          | DMA Bits |          | Receive              | Transmit             |  |  |

|----------|----------|----------|----------------------|----------------------|--|--|

| Bit [15] | Bit ]14] | Bit [13] |                      |                      |  |  |

| 0        | 0        | 0        | No DMA               | No DMA               |  |  |

| 0        | 0        | 1        | DMA0 or 2 (See Note) | DMA1 or 3 (See Note) |  |  |

| 0        | 1        | 0        | DMA1 or 3 (See Note) | DMA0 or 2 (See Note) |  |  |

| 0        | 1        | 1        | Reserved             | Reserved             |  |  |

| 1        | 0        | 0        | DMA0 or 2 (See Note) | No DMA               |  |  |

| 1        | 0        | 1        | DMA1 or 3 (See Note) | No DMA               |  |  |

| 1        | 1        | 0        | No DMA               | DMA0 or 2 (See Note) |  |  |

| 1        | 1        | 1        | No DMA               | DMA1 or 3 (See Note) |  |  |

*Note:* Serial channels 0 and 1 use DMA 0 and 1, while serial channels 2 and 3 use DMA 2 and 3.

| Mode | Description | Parity I  | Disable     | Parity E  | Enabled     | Stop Bits |

|------|-------------|-----------|-------------|-----------|-------------|-----------|

|      |             | Data Bits | Parity Bits | Data Bits | Parity Bits |           |

| 0    | Reserved    | ///       | ///         | ///       | ///         | ///       |

| 1    | Mode 1      | 8         | 0           | 7         | 1           | 1         |

| 2    | Mode 2      | 9         | 0           | N/A       | N/A         | 1         |

| 3    | Mode 3      | 9         | 0           | 8         | 1           | 1         |

| 4    | Mode 4      | 7         | 0           | N/A       | N/A         | 1         |

| 5    | Mode 5      | 8         | 0           | 7         | 1           | 2         |

| 6    | Reserved    | ///       | ///         | ///       | ///         | ///       |

| 7    | Reserved    | ///       | ///         | ///       | ///         | ///       |

#### Table 17. Serial Port Operating Mode Settings

# Programmable Input/Output

# **Overview**

This chapter describes the DSTni Programmable Input/Output (PIO) functions. Topics include:

- Theory of Operation on page 19

- PIO Register Summary on page 21

- PIO Register Definitions on page 21

- •

# Theory of Operation

### **PIO Functions**

DSTni's PIO can be configured for input, output, or alternate pin sharing (normal operation). On reset, all pins default to PIO input with weak pull-ups. Table 18 lists the possible modes and directions. Weak internal pull-up resistors are roughly 56K to 122K Ohms.

| PIO Mode      | <b>PIO Direction</b> | PIO Configuration                |

|---------------|----------------------|----------------------------------|

| 0             | 0                    | Normal output operation          |

| 0             | 1                    | PIO input with internal pull-up* |

| 1             | 0                    | PIO output                       |

| 1             | 1                    | PIO input with internal pull-up  |

| * Reset state | •                    |                                  |

#### Table 18. Parallel Port Functions

The 32 PIO signals can individually operate as open drain (collector) outputs by writing a 0 to the designated bit in the Data register and a 1 to the designated bit in the Mode register. Then:

- Writing a 1 in the Direction register disables the output.

- Writing a 0 in the Direction register drives the pin LOW.

- ٠

# **PIO Sharing Designations**

Error! Reference source not found. lists the PIO sharing designations.

| PIO Number | Shared Function Name | Power-On Reset Function                  |

|------------|----------------------|------------------------------------------|

|            | TMRIN1               |                                          |

| 0          | TMRINT<br>TMROUT1    | Input with pull-up<br>Input with pull-up |

| -          |                      |                                          |

| 2          | PCS6#                | Input with pull-up                       |

| 3          | PCS5#                | Input with pull-up                       |

| 4          | PCS4#                | Input with pull-up                       |

| 5          | PCS7#                | Input with pull-up                       |

| 6          | ARDY                 | Input with pull-up                       |

| 7          | DRQ2                 | Input with pull-up                       |

| 8          | DRQ3                 | Input with pull-up                       |

| 9          | NMI                  | Input with pull-up                       |

| 10         | TMROUT0              | Input with pull-up                       |

| 11         | TMRIN0               | Input with pull-up                       |

| 12         | DRQ0                 | Input with pull-up                       |

| 13         | I <sup>2</sup> CDTA  | Input with pull-up                       |

| 14         | CAN1TX               | Input with pull-up                       |

| 15         | CAN1RX               | Input with pull-up                       |

| 16         | LOCK#/SRDYOUT        | Input with pull-up                       |

| 17         | HOLD                 | Input with pull-up                       |

| 18         | CTS3#/SLVSEL#        | Input with pull-up (see Note below)      |

| 19         | RTS3#/SCK            | Input with pull-up (see Note below)      |

| 20         | RTS2#                | Input with pull-up                       |

| 21         | CTS2#                | Input with pull-up                       |

| 22         | TXD2                 | Input with pull-up                       |

| 23         | RXD2                 | Input with pull-up                       |

| 24         | MCS2#                | Input with pull-up                       |

| 25         | MCS3#                | Input with pull-up                       |

| 26         | A23                  | Input with pull-up                       |

| 27         | TXD3/SD0             | Input with pull-up (see Note below)      |

| 28         | RXD3/SDI             | Input with pull-up (see Note below)      |

| 29         | DRQ1                 | Input with pull-up                       |

| 30         | INT5#                | Input with pull-up                       |

| 31         | I <sup>2</sup> CCLK  | Input with pull-up                       |

|            |                      | 1                                        |

#### **Table 19. PIO Sharing Designations**

**Note:** PIO pins 18, 19, 27, and 28 are shared between serial port 2 and SPI, as selected by the SPIEN bit of the DSTni Configuration register.

# **PIO Register Summary**

### Table 20. PIO Register Summary

| Hex<br>Offset | Mnemonic | Register Description      | Page |

|---------------|----------|---------------------------|------|

| 7A            | PDATA1   | Parallel Port 1 Data      | 21   |

| 78            | PDIR1    | Parallel Port 1 Direction | 22   |

| 76            | PIOMODE1 | Parallel Port 1 Mode      | 23   |

| 74            | PDATA0   | Parallel Port 0 Data      | 23   |

| 72            | PDIR0    | Parallel Port 0 Direction | 24   |

| 70            | PIOMODE0 | Parallel Port 0 Mode      | 24   |

# **PIO Register Definitions**

## Parallel Port 1 Data Register

Note: The reset value of this register's bits is indeterminate.

#### Table 21. Parallel Port 1 Data Register

| BIT    | 15 | 14 | 13 | 12 | 11 | 10 | 9   | 8    | 7      | 6  | 5  | 4  | 3  | 2  | 1  | 0  |

|--------|----|----|----|----|----|----|-----|------|--------|----|----|----|----|----|----|----|

| OFFSET |    |    |    |    |    |    |     | 7Ał  | ו      |    |    |    |    |    |    |    |

| FIELD  |    |    |    |    |    |    | PIO | DATA | (31:16 | 6) |    |    |    |    |    |    |

| RESET  | _  |    | _  | _  | _  |    |     |      |        | _  |    |    |    |    | _  |    |

| RW     | RW | RW | RW | RW | RW | RW | RW  | RW   | RW     | RW | RW | RW | RW | RW | RW | RW |

#### Table 22. Parallel Port 1 Data Register Definitions

| Bits | Field Name       | Description                                                                                                                                                                                                                                               |

|------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15:0 | PIO DATA (31:16) | <b>Data</b><br>When a PIO is configured as an output the corresponding value in the PIO<br>Data register is driven out to the pin. For PIO pins configured as inputs, the<br>value on the pin is reflected on the corresponding bit in the Data register. |

# Parallel Port 1 Direction Register

| BIT                                 | 15                  | 14    | 13   | 12       | 11       | 10  | 9     | 8     | 7    | 6      | 5     | 4     | 3         | 2             | 1    | 0             |

|-------------------------------------|---------------------|-------|------|----------|----------|-----|-------|-------|------|--------|-------|-------|-----------|---------------|------|---------------|

| OFFSET                              |                     |       |      |          |          |     |       | 7     | 78h  |        |       |       |           |               |      |               |

| FIELD                               |                     |       |      |          |          |     | PIO I | DIREC | TION | (31:16 | 5)    |       |           |               |      |               |

| RESET                               | 1                   | 1     | 1    | 1        | 1        | 1   | 1     | 1     | 1    | 1      | 1     | 1     | 1         | 1             | 1    | 1             |

| RW                                  | RW                  | RW    | RW   | RW       | RW       | RW  | RW    | RW    | RW   | RW     | RW    | RW    | RW        | RW            | RW   | RW            |

| PIO<br>SHARING<br>DESIG-<br>NATIONS | I <sup>2</sup> CCLK | INT5# | DRQ1 | RXD3\SDI | TXD3/SD0 | A23 | MCS3# | MCS2# | RXD2 | TXD2   | CTS2# | RTS2# | RTS3#/SCK | CTS3#/SLVSEL# | НОГР | LOCK#/SRDYOUT |

#### Table 23. Parallel Port 1 Direction Register

### Table 24. Parallel Port 1 Direction Register Definitions

| Bits | Field Name    | Description                                                                                                                                             |

|------|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15:0 | PIO DIRECTION | Direction                                                                                                                                               |

|      | (31:16)       | Works with the PIO Mode register to determine the direction of each individual user-programmable IO.<br>1 = input ( <i>default</i> ).<br>0 = is output. |

# Parallel Port 1 Mode Register

| BIT                                 | 15                  | 14    | 13   | 12       | 11       | 10  | 9     | 8     | 7       | 6    | 5     | 4     | 3         | 2             | 1    | 0             |

|-------------------------------------|---------------------|-------|------|----------|----------|-----|-------|-------|---------|------|-------|-------|-----------|---------------|------|---------------|

| OFFSET                              |                     |       |      |          |          |     |       | 74    | 1h      |      |       |       |           |               |      |               |

| FIELD                               |                     |       |      |          |          |     | PIC   |       | )E (31: | 16)  |       |       |           |               |      |               |

| RESET                               | 0                   | 0     | 0    | 0        | 0        | 0   | 0     | 0     | 0       | 0    | 0     | 0     | 0         | 0             | 0    | 0             |

| PIO<br>SHARING<br>DESIG-<br>NATIONS | I <sup>2</sup> CCLK | INT5# | DRQ1 | RXD3\SDI | TXD3/SD0 | A23 | MCS3# | MCS2# | RXD2    | TXD2 | CTS2# | RTS2# | RTS3#/SCK | CTS3#/SLVSEL# | НОГД | LOCK#/SRDYOUT |

#### Table 25. Parallel Port 1 Mode Register

#### Table 26. Parallel Port 1 Mode Register Definitions

| Bits | Field Name       | Description                                                                                                                                        |

|------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| 15:0 | PIO MODE (31:16) | <b>Mode</b><br>Works with the PIO Direction register to determine the configuration of each<br>individual user-programmable IO. Default mode is 0. |

### Parallel Port 0 Data Register

*Note:* The reset value of this register's bits is indeterminate.

### Table 27. Parallel Port 0 Data Register

| BIT    | 15 | 14 | 13 | 12 | 11 | 10 | 9  | 8     | 7     | 6   | 5 | 4 | 3 | 2 | 1 | 0 |

|--------|----|----|----|----|----|----|----|-------|-------|-----|---|---|---|---|---|---|

| OFFSET |    |    |    |    |    |    |    | 74    | h     |     |   |   |   |   |   |   |